Hi,

I would like to ask some questions on the writing of an ISFP (Interrupt Service Fetch Packet). By "versatile" I mean the ISFP uses register branch the range is not restricted to a constant displacement. All questions revolve around an example 6455 Starter Project.zip which Brad Griffis posted on 10-19-2009. Although the post originally appeared in DaVinci Processor Forum, all the critical issues of the problem relates more closely to CPU architecture and assembly language, so I choose to post it here first.

I have some questions on the above regarding ISTP (Interrupt Service Fetch Packet):

Question I:

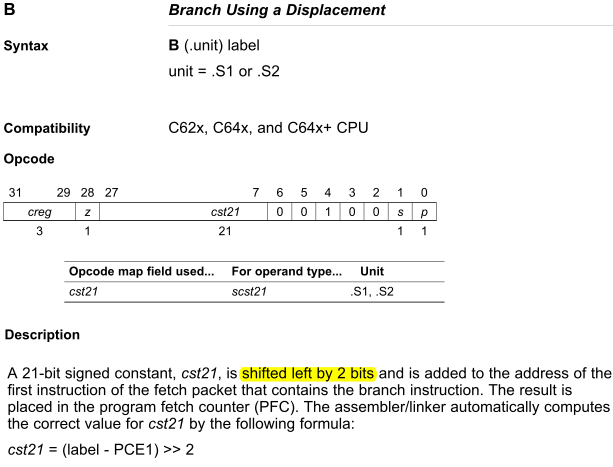

Branch using a displacement has a 21 bit constant, which will be shifted left by 2 bits to generate the address. Therefore, it should be 23 bits address, 2^23=8MB, not 4MB.

Question II:

Does Brad mean a singular "content" rather than the plural "contents"? There is only one register to save and restore during this.

Question III:

Each ISFP (Interrupt Service Fetch Packet) should be exactly 8 words long, so can the "diligent" version, in contrary to his "lazy" version, be fit into the 8 words long packet, especially when .nocmp is used to prevent compact instruction from being used?

I tried to complete the “due diligence” below, and in the code R could be any arbitrary general purpose register:

stw R, *--SP

;

Stack grow lower, store

mvkl target_address, R

;

Low 16 bit

mvkh target_address, R

;

High 16 bit

b R

;

Branching using a register

ldw *SP++, R

;

Restore

nop 2

;

nop 1

;

2+1+1 = 4 delay slots = delay (ldw);

nop 1

;

1(ldw)+2+2+1 = 5 delay slots = delay (b)

I probably made a mistake with SP: I am not familiar with assembly and assumed SP points to the top element of the stack, but I have also read elsewhere that SP points to the address over (logically; physically below) the top element. If this is the case, then the code has to be modified accordingly.

Could anyone comment on the all the questions above? And please point out if my code has any problem.

And I still have an additional question: is there a register dedicated as stack pointer? Are there assembly commands or CPU instructions provided specifically for push and pop? I searched the spru732j, TMS320C64x-C64x+ DSP CPU and Instruction Set Reference Guide, but didn't find any.

Zheng