Hi,

I'm using the am243x-EVM.

I would like to execute my program from DDR with cache enabled.

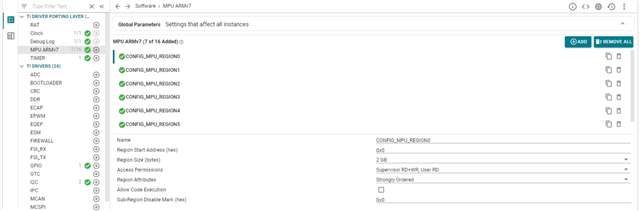

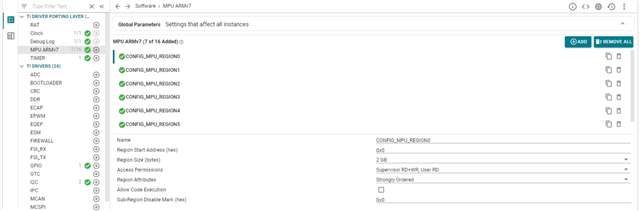

Here is my syscfg picture.

I've noticed that on the very first entry there seems to be no cache

Should I delete it or define in other way ?

Thanks,

Eli

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I'm using the am243x-EVM.

I would like to execute my program from DDR with cache enabled.

Here is my syscfg picture.

I've noticed that on the very first entry there seems to be no cache

Should I delete it or define in other way ?

Thanks,

Eli

Hi Eli,

The way the MPU entries in the MPU ARMv7 is the following entries overwrites the previous ones. For example, the first entry (REGION 0) sets the 2GB address space start from 0 to "Strongly Ordered". The second entry (REGION 1) sets the 32KB address space start at 0 to "Cached". Since the 2nd entry overwrites the first one, so the 32KB starting at 0 will be set to "Cached". The rest of the 2GB-32KB address space starting at 0x8000 will keep its "Strongly Ordered". This rule applies to the entries 3 to 6 in order.

Best regards,

Ming

Hi Ming,

Sorry about the double-question - just pressed Post again

So if I have the DDR region 0x80000000 cached - does it mean that the program executed from DDR is using cache ?

I thought I should see some lines like CacheP_init (.. somewhere in the drivers !

I'm interested in cache to speed up the performance.

Maybe I should also add some flag to optimize the code for speed ?

Thanks,

Best Regards,

Eli

Hi Eli,

Yes. If you set the DDR into cached mode, then the Icache (32KB) and Dcache (32KB) will be used automatically by ARM cores to take advantage of the code or data locality. You do not need to add any flags.

CacheP_xxx can be used to force certain cache operation explicitly.

Best regards,

Ming

Hi Ming,

I found CacheP_getEnabled(); function - returning the cache mode.

I get the value 3 which , if I'm correct , means that L1 cache is enabled.

#define CacheP_TYPE_L1P (0x0001u) /**< L1 program cache */

#define CacheP_TYPE_L1D (0x0002u) /**< L1 data cache */

#define CacheP_TYPE_L1((CacheP_TYPE_L1P)|(CacheP_TYPE_L1D)) /**< All L1 cache's */

How can I enable also L2 cache ?

Thanks,

Best Regards,

Eli