Hi,

I would like to ask a question on opcode.

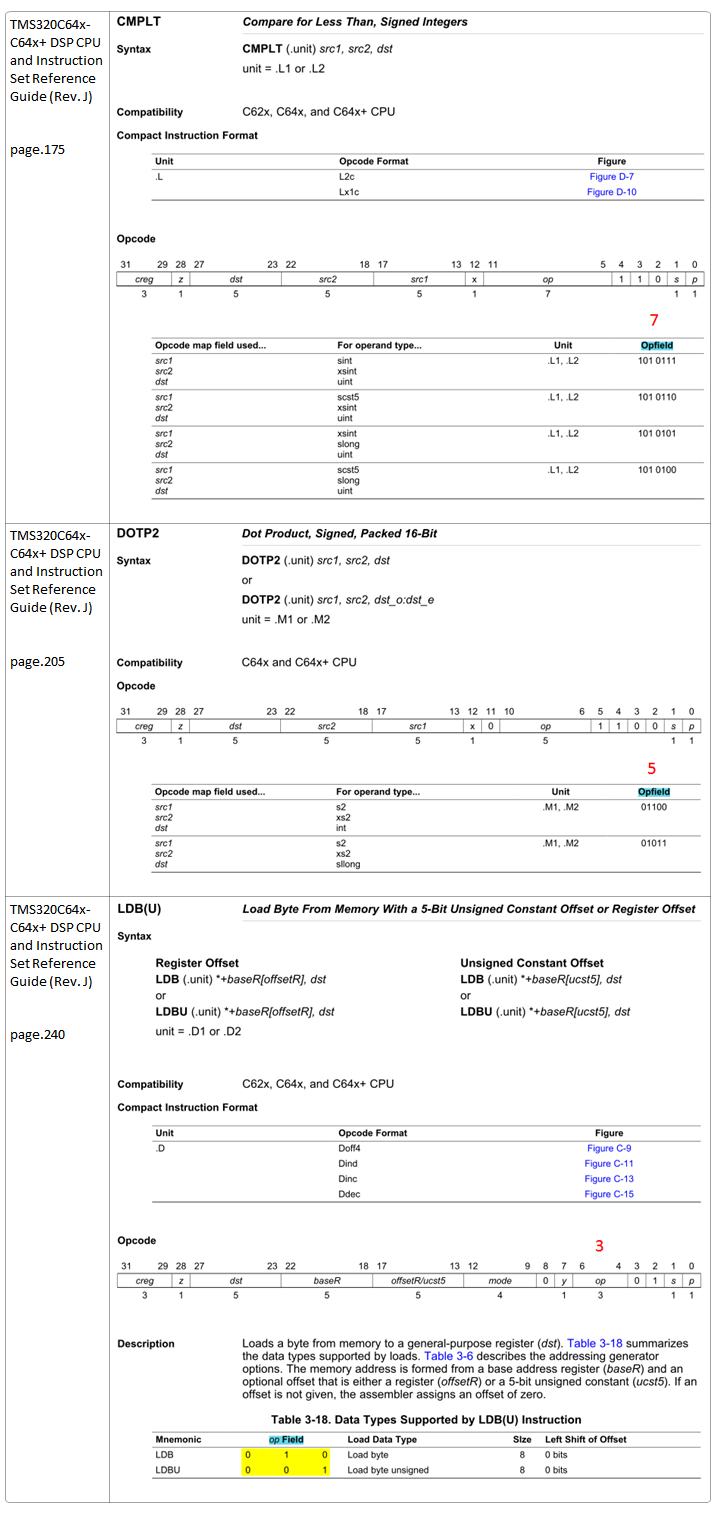

I noticed that opfield on C64x are of varied length, and are at different position within opcode.

In instructions above, opfield's lengths are 7, 5, and 3 bits; their starting bit are 5th, 6th and 4th bit.

http://en.wikipedia.org/wiki/Opcode said:In computer science, an opcode (operation code) is the portion of a machine language instruction that specifies the operation to be performed. Their specification and format are laid out in the instruction set architecture of the processor in question (which may be a general CPU or a more specialized processing unit). Apart from the opcode itself, an instruction normally also has one or more specifiers for operands (i.e. data) on which the operation should act, although some operations may have implicit operands, or none at all. There are instruction sets with nearly uniform fields for opcode and operand specifiers, as well as others (the x86 architecture for instance) with a more complicated, varied length structure. [1]

From the above observation C64x is obviously of varied opfield design. In execution, how does the CPU know where within each 32bit opcode to find the opfield?

Zheng