Hi All,

I have a question on stack alignment for C code compiled for C66xx devices. I need to have 16 byte aligned data structures for local storage (stack) within functions. According to the "cl6x compiler guide":

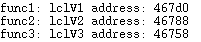

This statement is a bit confusing in that it is claiming that the C6600 stack alignment is 16 bytes but the C6400/C6400+/C6740/C6600 ISAs align the stack to 8 bytes. I'm seeing the simulation results of the C6670 ISS model align the stack on 8 byte boundaries on function calls even when I use the __x128_t type for a local variable. The executable module I'm building is composed of all C6600 objects compiled with the -mv6600 option. How do I enforce a 16 byte stack boundary?

Thanks,

Mark Brown