Other Parts Discussed in Thread: UNIFLASH

Tool/software:

Hello TI experts,

Running into some issues regarding load and run adress settings in CCS.

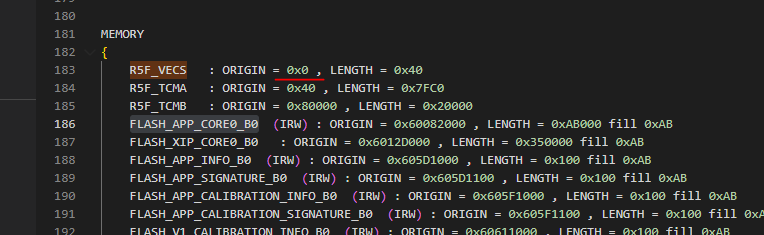

With the current TI toolchain, when a .appimage/.MCELF is generated, the physical/load adress is ignored, sections are a) ordered by RAM/run adress and b) merged together into a single 'blob' of data, which is then flashed to a particular flash offset.

To give some purpose/aim behind the question, essentially we want to control where certain sections end up in the .mcelf and subsequently in flash memory, especially calibration sections. This is to be able to do checksums/hashing on individual sections. Ideally this would be done through control of the load adress for each section.

When I try configuring flash-based load adresses in CCS for sections, the CCS debugger seems to interpret these as the RAM/run adresses, causing CCS debugger to not work.

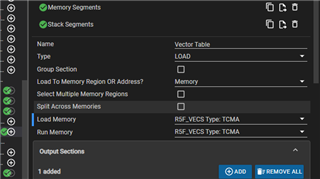

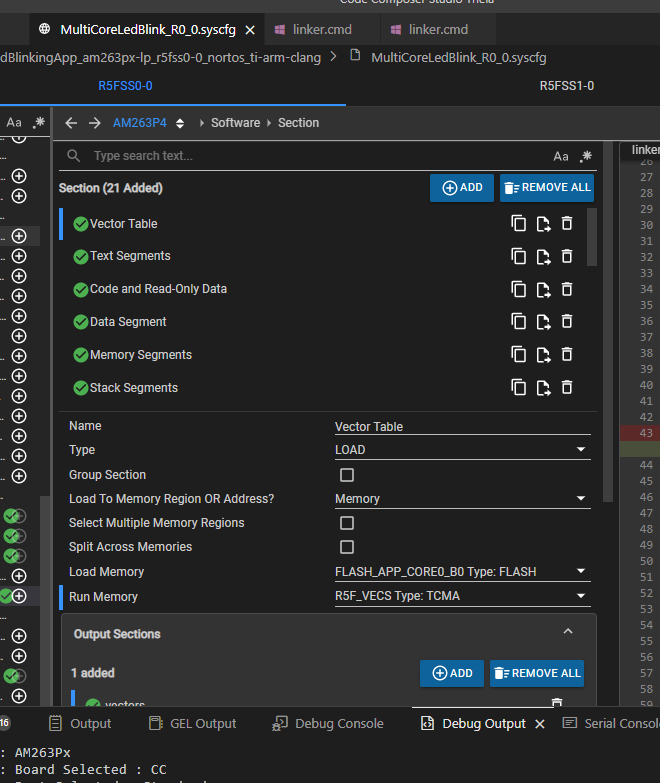

For example, if I use the default load/run adresses for the vector table (0x0 into TCMA), the CCS debugger can program this section as required:

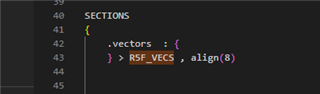

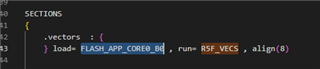

Linker:

Running CCS debugger:

If I update the load adress to be flash-based:

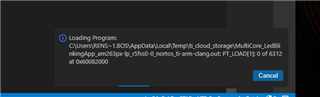

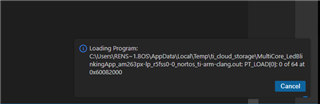

Running CCS debugger:

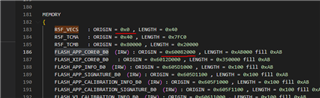

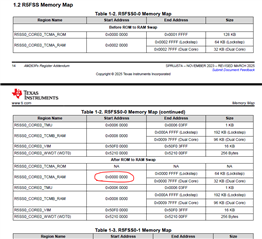

As visible, for option 2 (i.e setting the load adress to be flash-based), CCS debugger now cannot program the Vectors section (PT_LOAD[0]) anymore. Looking at memory map:

presumably as now the section is not placed into R5SS0_CORE0_TCMA_RAM anymore.

So it seems to me like CCS debugger uses section load adresses as the adress where a section needs to be run. Which would seem counterintuitive, as this essentially makes the 'load adress' option for all sections useless - as CCS debugger doesn't work.

Is this assumption correct? Is there a reason for CCS debugger not using the RAM/run adress for debug purposes? Is there anyway to make CCS debugger use run adresses instead of load adresses for debug?

Thanks,

Rens