Part Number: CODECOMPOSER

Other Parts Discussed in Thread: CCSTUDIO, MSPM0C1104

I have same symptom with this (https://e2e.ti.com/support/tools/code-composer-studio-group/ccs/f/code-composer-studio-forum/1448946/codecomposer-thiea-clangd-fails-to-recognize-some-functions-in-the-same-header)

So I traced what is problem

Version info

Details

Version: 20.4.1.4__1.10.1

Default VS Code API: 1.102.3

VS Code Compatibility

List of extensions

@ccs/ccstudio 20.4.0

@ccs/ccstudio-debug 20.4.0

@ccs/ccstudio-getting-started 20.4.0

@ccs/ccstudio-guicomposer 20.4.0

@ccs/ccstudio-plugin 20.4.0

@ccs/ccstudio-project 20.4.0

@ccs/ccstudio-support 20.4.0

@ccs/ccstudio-trace-config 20.4.0

@ccs/ccstudio-trace-viewer 20.4.0

@ccs/ccstudio-updater 20.4.0

@theia/ai-anthropic 1.64.1

@theia/ai-chat 1.64.1

@theia/ai-chat-ui 1.64.1

@theia/ai-code-completion 1.64.1

@theia/ai-core 1.64.1

@theia/ai-core-ui 1.64.1

@theia/ai-editor 1.64.1

@theia/ai-google 1.64.1

@theia/ai-history 1.64.1

@theia/ai-huggingface 1.64.1

@theia/ai-ide 1.64.1

@theia/ai-llamafile 1.64.1

@theia/ai-mcp 1.64.1

@theia/ai-mcp-ui 1.64.1

@theia/ai-ollama 1.64.1

@theia/ai-openai 1.64.1

@theia/ai-scanoss 1.64.1

@theia/ai-terminal 1.64.1

@theia/ai-vercel-ai 1.64.1

@theia/api-provider-sample 1.64.1

@theia/bulk-edit 1.64.1

@theia/callhierarchy 1.64.1

@theia/collaboration 1.64.1

@theia/console 1.64.1

@theia/core 1.64.1

@theia/debug 1.64.1

@theia/dev-container 1.64.1

@theia/editor 1.64.1

@theia/editor-preview 1.64.1

@theia/electron 1.64.1

@theia/external-terminal 1.64.1

@theia/file-search 1.64.1

@theia/filesystem 1.64.1

@theia/keymaps 1.64.1

@theia/markers 1.64.1

@theia/messages 1.64.1

@theia/metrics 1.64.1

@theia/mini-browser 1.64.1

@theia/monaco 1.64.1

@theia/navigator 1.64.1

@theia/notebook 1.64.1

@theia/outline-view 1.64.1

@theia/output 1.64.1

@theia/plugin-dev 1.64.1

@theia/plugin-ext 1.64.1

@theia/plugin-ext-headless 1.64.1

@theia/plugin-ext-vscode 1.64.1

@theia/preferences 1.64.1

@theia/preview 1.64.1

@theia/process 1.64.1

@theia/property-view 1.64.1

@theia/remote 1.64.1

@theia/remote-wsl 1.64.1

@theia/scanoss 1.64.1

@theia/scm 1.64.1

@theia/scm-extra 1.64.1

@theia/search-in-workspace 1.64.1

@theia/secondary-window 1.64.1

@theia/task 1.64.1

@theia/terminal 1.64.1

@theia/test 1.64.1

@theia/timeline 1.64.1

@theia/toolbar 1.64.1

@theia/typehierarchy 1.64.1

@theia/userstorage 1.64.1

@theia/variable-resolver 1.64.1

@theia/vsx-registry 1.64.1

@theia/workspace 1.64.1

Project imported / empty_driverlib_src / MSPM0C1104

Here is what I done :

added clangd launch argument --log=verbose

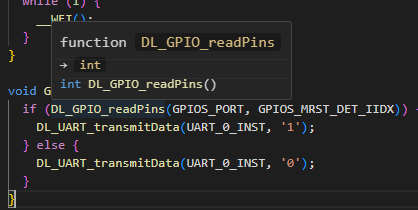

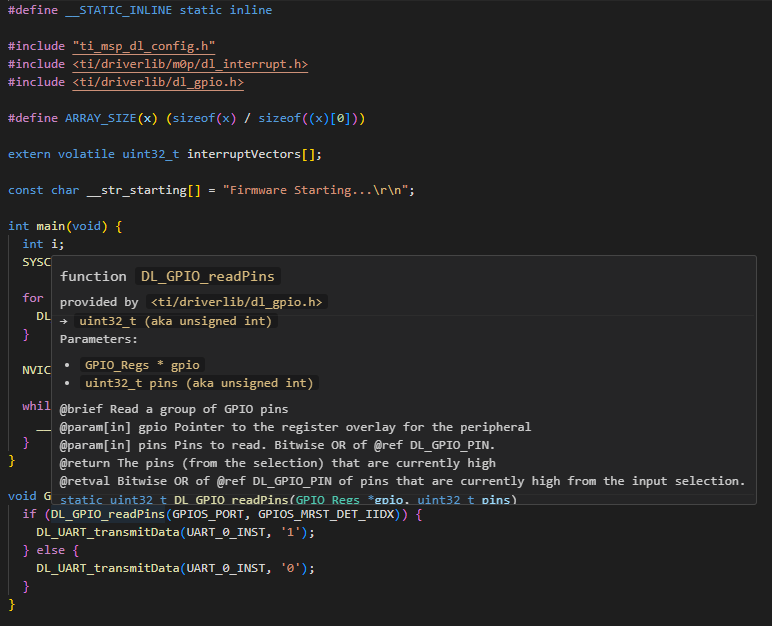

Then I can verify compiler that launched from clangd doesn't recognize __STATIC_INLINE macro

V[20:22:59.903] <<< {"id":189,"jsonrpc":"2.0","method":"shutdown"}

I[20:22:59.903] <-- shutdown(189)

I[20:22:59.903] --> reply:shutdown(189) 0 ms

V[20:22:59.903] >>> {"id":189,"jsonrpc":"2.0","result":null}

V[20:22:59.904] <<< {"jsonrpc":"2.0","method":"exit"}

I[20:22:59.904] <-- exit

I[20:22:59.904] LSP finished, exiting with status 0

I[20:22:59.945] clangd version 19.1.2 (github.com/.../llvm-project 7ba7d8e2f7b6445b60679da826210cdde29eaf8b)

I[20:22:59.947] Features: windows+grpc

I[20:22:59.947] PID: 41016

I[20:22:59.947] Working directory: c:\Users\hsjung\Desktop\ccs_workspace\LukusCB-SUPV

I[20:22:59.947] argv[0]: C:\ti\ccs2041\ccs\theia\resources\clangd\clangd.exe

I[20:22:59.947] argv[1]: --log=verbose

I[20:22:59.947] argv[2]: -header-insertion=never

I[20:22:59.947] argv[3]: -limit-results=200

V[20:22:59.954] User config file is C:\Users\hsjung\AppData\Local\clangd\config.yaml

I[20:22:59.954] Starting LSP over stdin/stdout

V[20:22:59.954] <<< {"id":0,"jsonrpc":"2.0","method":"initialize","params":{"capabilities":{"general":{"markdown":{"parser":"marked","version":"1.1.0"},"positionEncodings":["utf-16"],"regularExpressions":{"engine":"ECMAScript","version":"ES2020"},"staleRequestSupport":{"cancel":true,"retryOnContentModified":["textDocument/semanticTokens/full","textDocument/semanticTokens/range","textDocument/semanticTokens/full/delta"]}},"notebookDocument":{"synchronization":{"dynamicRegistration":true,"executionSummarySupport":true}},"textDocument":{"callHierarchy":{"dynamicRegistration":true},"codeAction":{"codeActionLiteralSupport":{"codeActionKind":{"valueSet":["","quickfix","refactor","refactor.extract","refactor.inline","refactor.rewrite","source","source.organizeImports"]}},"dataSupport":true,"disabledSupport":true,"dynamicRegistration":true,"honorsChangeAnnotations":false,"isPreferredSupport":true,"resolveSupport":{"properties":["edit"]}},"codeLens":{"dynamicRegistration":true},"colorProvider":{"dynamicRegistration":true},"completion":{"completionItem":{"commitCharactersSupport":true,"deprecatedSupport":true,"documentationFormat":["markdown","plaintext"],"insertReplaceSupport":true,"insertTextModeSupport":{"valueSet":[1,2]},"labelDetailsSupport":true,"preselectSupport":true,"resolveSupport":{"properties":["documentation","detail","additionalTextEdits"]},"snippetSupport":true,"tagSupport":{"valueSet":[1]}},"completionItemKind":{"valueSet":[1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25]},"completionList":{"itemDefaults":["commitCharacters","editRange","insertTextFormat","insertTextMode"]},"contextSupport":true,"dynamicRegistration":true,"editsNearCursor":true,"insertTextMode":2},"declaration":{"dynamicRegistration":true,"linkSupport":true},"definition":{"dynamicRegistration":true,"linkSupport":true},"diagnostic":{"dynamicRegistration":true,"relatedDocumentSupport":false},"documentHighlight":{"dynamicRegistration":true},"documentLink":{"dynamicRegistration":true,"tooltipSupport":true},"documentSymbol":{"dynamicRegistration":true,"hierarchicalDocumentSymbolSupport":true,"labelSupport":true,"symbolKind":{"valueSet":[1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26]},"tagSupport":{"valueSet":[1]}},"foldingRange":{"dynamicRegistration":true,"foldingRange":{"collapsedText":false},"foldingRangeKind":{"valueSet":["comment","imports","region"]},"lineFoldingOnly":true,"rangeLimit":5000},"formatting":{"dynamicRegistration":true},"hover":{"contentFormat":["markdown","plaintext"],"dynamicRegistration":true},"implementation":{"dynamicRegistration":true,"linkSupport":true},"inactiveRegionsCapabilities":{"inactiveRegions":true},"inlayHint":{"dynamicRegistration":true,"resolveSupport":{"properties":["tooltip","textEdits","label.tooltip","label.location","label.command"]}},"inlineValue":{"dynamicRegistration":true},"linkedEditingRange":{"dynamicRegistration":true},"onTypeFormatting":{"dynamicRegistration":true},"publishDiagnostics":{"codeDescriptionSupport":true,"dataSupport":true,"relatedInformation":true,"tagSupport":{"valueSet":[1,2]},"versionSupport":false},"rangeFormatting":{"dynamicRegistration":true},"references":{"dynamicRegistration":true},"rename":{"dynamicRegistration":true,"honorsChangeAnnotations":true,"prepareSupport":true,"prepareSupportDefaultBehavior":1},"selectionRange":{"dynamicRegistration":true},"semanticTokens":{"augmentsSyntaxTokens":true,"dynamicRegistration":true,"formats":["relative"],"multilineTokenSupport":false,"overlappingTokenSupport":false,"requests":{"full":{"delta":true},"range":true},"serverCancelSupport":true,"tokenModifiers":["declaration","definition","readonly","static","deprecated","abstract","async","modification","documentation","defaultLibrary"],"tokenTypes":["namespace","type","class","enum","interface","struct","typeParameter","parameter","variable","property","enumMember","event","function","method","macro","keyword","modifier","comment","string","number","regexp","operator","decorator"]},"signatureHelp":{"contextSupport":true,"dynamicRegistration":true,"signatureInformation":{"activeParameterSupport":true,"documentationFormat":["markdown","plaintext"],"parameterInformation":{"labelOffsetSupport":true}}},"synchronization":{"didSave":true,"dynamicRegistration":true,"willSave":true,"willSaveWaitUntil":true},"typeDefinition":{"dynamicRegistration":true,"linkSupport":true},"typeHierarchy":{"dynamicRegistration":true}},"window":{"showDocument":{"support":true},"showMessage":{"messageActionItem":{"additionalPropertiesSupport":true}},"workDoneProgress":true},"workspace":{"applyEdit":true,"codeLens":{"refreshSupport":true},"configuration":true,"diagnostics":{"refreshSupport":true},"didChangeConfiguration":{"dynamicRegistration":true},"didChangeWatchedFiles":{"dynamicRegistration":true,"relativePatternSupport":true},"executeCommand":{"dynamicRegistration":true},"fileOperations":{"didCreate":true,"didDelete":true,"didRename":true,"dynamicRegistration":true,"willCreate":true,"willDelete":true,"willRename":true},"inlayHint":{"refreshSupport":true},"inlineValue":{"refreshSupport":true},"semanticTokens":{"refreshSupport":true},"symbol":{"dynamicRegistration":true,"resolveSupport":{"properties":["location.range"]},"symbolKind":{"valueSet":[1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26]},"tagSupport":{"valueSet":[1]}},"workspaceEdit":{"changeAnnotationSupport":{"groupsOnLabel":true},"documentChanges":true,"failureHandling":"textOnlyTransactional","normalizesLineEndings":true,"resourceOperations":["create","rename","delete"]},"workspaceFolders":true}},"clientInfo":{"name":"Code Composer Studio","version":"1.102.3"},"initializationOptions":{"clangdFileStatus":true,"fallbackFlags":[]},"locale":"en","processId":2400,"rootPath":"c:\\Users\\hsjung\\Desktop\\ccs_workspace\\LukusCB-SUPV","rootUri":"file:///c%3A/Users/hsjung/Desktop/ccs_workspace/LukusCB-SUPV","trace":"off","workspaceFolders":[{"name":"LukusCB-SUPV","uri":"file:///c%3A/Users/hsjung/Desktop/ccs_workspace/LukusCB-SUPV"}]}}

I[20:22:59.954] <-- initialize(0)

I[20:22:59.989] --> reply:initialize(0) 34 ms

V[20:22:59.989] >>> {"id":0,"jsonrpc":"2.0","result":{"capabilities":{"astProvider":true,"callHierarchyProvider":true,"clangdInlayHintsProvider":true,"codeActionProvider":{"codeActionKinds":["quickfix","refactor","info"]},"compilationDatabase":{"automaticReload":true},"completionProvider":{"resolveProvider":false,"triggerCharacters":[".","<",">",":","\"","/","*"]},"declarationProvider":true,"definitionProvider":true,"documentFormattingProvider":true,"documentHighlightProvider":true,"documentLinkProvider":{"resolveProvider":false},"documentOnTypeFormattingProvider":{"firstTriggerCharacter":"\n","moreTriggerCharacter":[]},"documentRangeFormattingProvider":true,"documentSymbolProvider":true,"executeCommandProvider":{"commands":["clangd.applyFix","clangd.applyRename","clangd.applyTweak"]},"foldingRangeProvider":true,"hoverProvider":true,"implementationProvider":true,"inactiveRegionsProvider":true,"inlayHintProvider":true,"memoryUsageProvider":true,"referencesProvider":true,"renameProvider":{"prepareProvider":true},"selectionRangeProvider":true,"semanticTokensProvider":{"full":{"delta":true},"legend":{"tokenModifiers":["declaration","definition","deprecated","deduced","readonly","static","abstract","virtual","dependentName","defaultLibrary","usedAsMutableReference","usedAsMutablePointer","constructorOrDestructor","userDefined","functionScope","classScope","fileScope","globalScope"],"tokenTypes":["variable","variable","parameter","function","method","function","property","variable","class","interface","enum","enumMember","type","type","unknown","namespace","typeParameter","concept","type","macro","modifier","operator","bracket","label","comment"]},"range":false},"signatureHelpProvider":{"triggerCharacters":["(",")","{","}","<",">",","]},"standardTypeHierarchyProvider":true,"textDocumentSync":{"change":2,"openClose":true,"save":true},"typeDefinitionProvider":true,"typeHierarchyProvider":true,"workspaceSymbolProvider":true},"serverInfo":{"name":"clangd","version":"clangd version 19.1.2 (github.com/.../llvm-project 7ba7d8e2f7b6445b60679da826210cdde29eaf8b) windows+grpc x86_64-pc-windows-msvc"}}}

V[20:22:59.990] <<< {"jsonrpc":"2.0","method":"initialized","params":{}}

I[20:22:59.990] <-- initialized

V[20:22:59.992] <<< {"jsonrpc":"2.0","method":"textDocument/didOpen","params":{"textDocument":{"languageId":"c","text":"/*\n * Copyright (c) 2021, Texas Instruments Incorporated\n * All rights reserved.\n *\n * Redistribution and use in source and binary forms, with or without\n * modification, are permitted provided that the following conditions\n * are met:\n *\n * * Redistributions of source code must retain the above copyright\n * notice, this list of conditions and the following disclaimer.\n *\n * * Redistributions in binary form must reproduce the above copyright\n * notice, this list of conditions and the following disclaimer in the\n * documentation and/or other materials provided with the distribution.\n *\n * * Neither the name of Texas Instruments Incorporated nor the names of\n * its contributors may be used to endorse or promote products derived\n * from this software without specific prior written permission.\n *\n * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS \"AS IS\"\n * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,\n * THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR\n * PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR\n * CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,\n * EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,\n * PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;\n * OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,\n * WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR\n * OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,\n * EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.\n */\n\n// #define __STATIC_INLINE static inline\n\n#include \"ti_msp_dl_config.h\"\n#include <ti/driverlib/m0p/dl_interrupt.h>\n#include <ti/driverlib/dl_gpio.h>\n\n#define ARRAY_SIZE(x) (sizeof(x) / sizeof((x)[0]))\n\nextern volatile uint32_t interruptVectors[];\n\nconst char __str_starting[] = \"Firmware Starting...\\r\\n\";\n\nint main(void) {\n int i;\n SYSCFG_DL_init();\n\n for (i = 0; i < ARRAY_SIZE(__str_starting); i++) {\n DL_UART_transmitData(UART_0_INST, __str_starting[i]);\n }\n\n NVIC_EnableIRQ(GPIOS_INT_IRQN);\n\n while (1) {\n __WFI();\n }\n}\n\nvoid GPIOA_IRQHandler(void) {\n if (DL_GPIO_readPins(GPIOS_PORT, GPIOS_MRST_DET_IIDX)) {\n DL_UART_transmitData(UART_0_INST, '1');\n } else {\n DL_UART_transmitData(UART_0_INST, '0');\n }\n}","uri":"file:///c%3A/Users/hsjung/Desktop/ccs_workspace/LukusCB-SUPV/main.c","version":166}}}

I[20:22:59.992] <-- textDocument/didOpen