Part Number: AM2634-Q1

Hi Ti team,

we are developing application which core 0-0 and core 0-1 involved. Core 0-0 is responsible for application and core 0-1 responsible for the ethernet communication. The core 0-0 and core 0-1 is communication via safeIPC/notify IPC. We have prvided enough memory (OCRAM) for the both cores and we feel no memory overlap between them.

Issue:

when increasing the code of core 0-0 causes core 0-1 operation which means core 0-0 is working normal and core 0-1 is not at all running (i.e, we are printing the caracter after driversInit()). we have changed OCRAM start address and reduce the code size of core 0-0 but no use.

Questions:

1.Is any specific configuration shall follow to be use the core 0-0 and core 0-1?

2. What size of OCRAM can be used?

3. is SBL in OCRAM is OK are not ? if it is required what should be address of this?

4. in core 0-1 has the CPPI_DESC memory, where it can keep in OCRAM?

5. what should be minimum size of the OCRAM?

6. what size of OCRAM shall fix for OCRAM and should we keep any free space on OCRAM?

7. is any specific valus of stack and heep size shall followed?

Attachments:

Herewith we are attaching the images of our configuration and memory details. Kindly help us to come out of the issue...

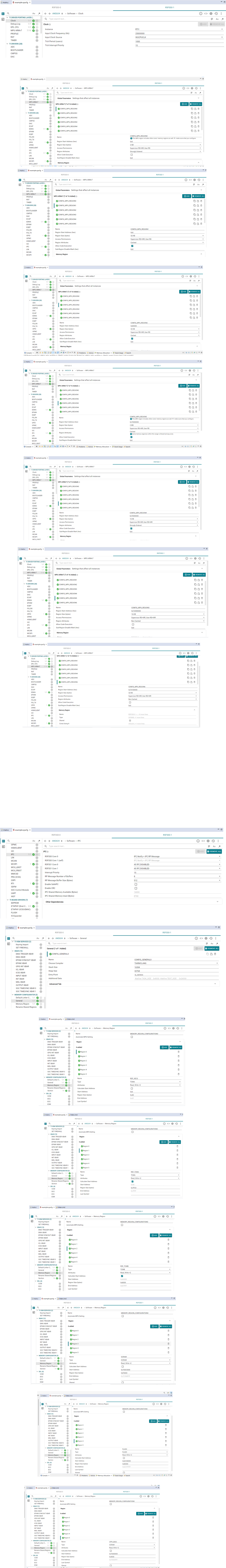

core 0-0- syscfg

linker.cmd:

core 0-0

MEMORY

{

R5F_VECS : ORIGIN = 0x0 , LENGTH = 0x40

R5F_TCMA : ORIGIN = 0x40 , LENGTH = 0x7FC0

R5F_TCMB : ORIGIN = 0x80000 , LENGTH = 0x8000

SBL : ORIGIN = 0x60000000 , LENGTH = 0x40000

OCRAM : ORIGIN = 0x70040000 , LENGTH = 0x80000

USER_SHM_MEM : ORIGIN = 0x701D0000 , LENGTH = 0x4000

LOG_SHM_MEM : ORIGIN = 0x701D4000 , LENGTH = 0x4000

FLASH : ORIGIN = 0x60100000 , LENGTH = 0x80000

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0x72000000 , LENGTH = 0x3E80

MAILBOX_HSM : ORIGIN = 0x44000000 , LENGTH = 0x3CE

MAILBOX_R5F : ORIGIN = 0x44000400 , LENGTH = 0x3CE

/* For memory Regions not defined in this core but shared by other cores with the current core */

}

core 0-1:

MEMORY

{

R5F_VECS : ORIGIN = 0x0 , LENGTH = 0x40

R5F_TCMA : ORIGIN = 0x40 , LENGTH = 0x7FC0

R5F_TCMB : ORIGIN = 0x80000 , LENGTH = 0x8000

OCRAM : ORIGIN = 0x700C5000 , LENGTH = 0xF0000

CPPI_DESC : ORIGIN = 0x70000000 , LENGTH = 0x4000

FLASH : ORIGIN = 0x60180000 , LENGTH = 0x80000

/* For memory Regions not defined in this core but shared by other cores with the current core */

USER_SHM_MEM : ORIGIN = 0x701D0000 , LENGTH = 0x4000

LOG_SHM_MEM : ORIGIN = 0x701D4000 , LENGTH = 0x4000

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0x72000000 , LENGTH = 0x3E80

MAILBOX_HSM : ORIGIN = 0x44000000 , LENGTH = 0x3CE

MAILBOX_R5F : ORIGIN = 0x44000400 , LENGTH = 0x3CE

}

find below core 0-0 syscfg

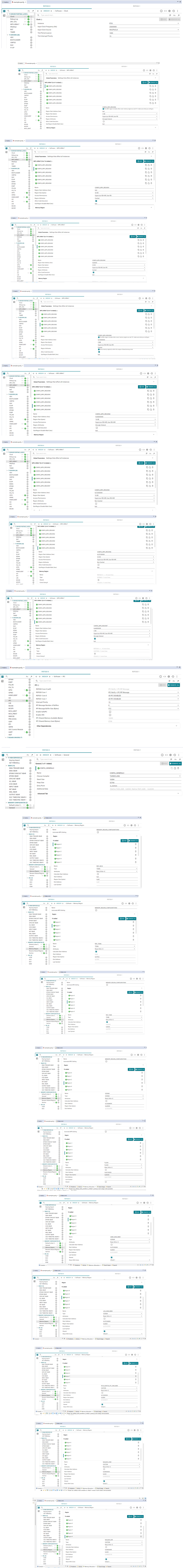

find below core 0-1 syscfg