Hello,

I have been trying to debug my application using code composer studio (Beagleboard XM/CCS : 5.2.0.00069 Linux/Opella XDS100V2)

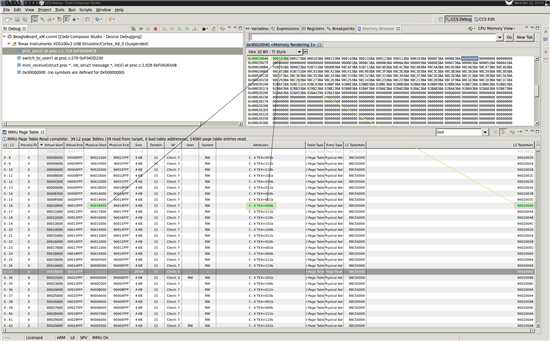

The attribute colomn of the MMU Page Table view shows the caching properties of the memory(Bufferent/Cached/Executable/ and the TEX attributes). When I compare the TEX attributes with what I write and what can be view in the physical memory view they look wrong.

In the attached example the value in memory is 0x900183BA and the value of TEX should be 110b. Also I see that the value of TEX is decremented every entry.

Is this a bug in CCS?