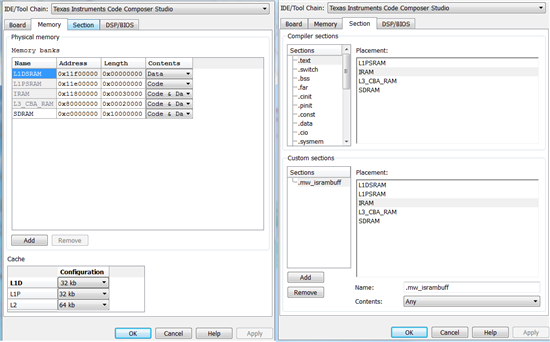

I have a simple question regarding the Profile Clock in Code Composer v3.3. I am using the OMAP L137 and Simulink to generate code for real time noise cancellation.

I want to measure the time it takes to run through an iteration of my code (it is an adaptive algorithm). From what I know, you do:

Time passed = cycles * (1/300MHz)

In the Clock Setup you can choose from: Cycles, CPU Execute Cycles, etc.

When I pick Cycles, I get cycles ranging in the 100,000s which translates to an unacceptable amount of latency.

When I pick CPU Execute Cycles, I get more reasonable cycles in the 1000s and below.

Which one do I choose to measure the the correct amount of cycles the DSP takes to execute the code?