Hi TI team,

we would like to set the timer 5 & 6 of AM335x,

but always fail.

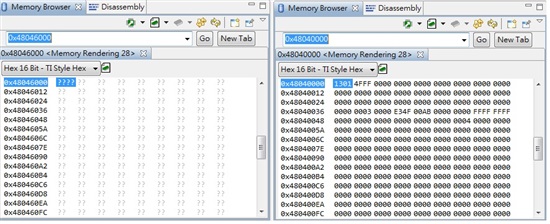

and then we found we can not access the registers of timer 5 & 6(the register address is 0x48046000),

but the register of timer 2 (the register address is 0x48040000) can be accessed.

and also CCS can not access the registers of timer 5 & 6.

are there not the registers of timer 5 & 6 with AM335x?