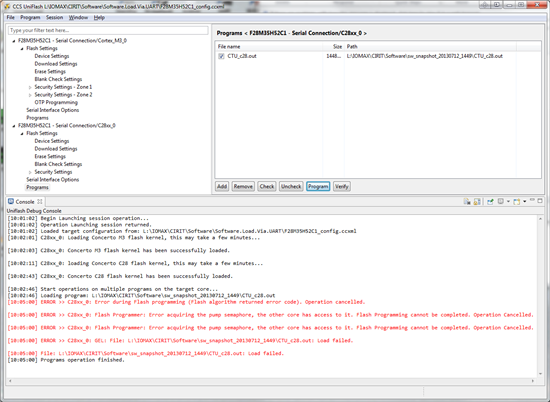

When trying to program the M3 core on a F28M35H52C1RFPT and I get the follwing error:

"The calculated system clock (75 MHz) is higher than the maximum allowed value (60 MHz). Operation Cancelled."

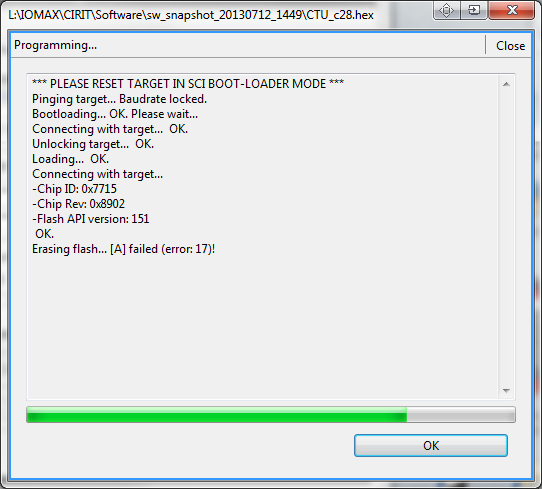

I get a similar error when I try to program the C28 core:

"The calculated system clock (150 MHz) is higher than the maximum allowed value (60 MHz). Operation Cancelled."

This happens on 2 boards which I have had the MCU replaced. My other 4 development boards program without a problem. Is there a problem with the MCU's?