I have a program which is failing when initializing an array to zero, ie:

char data[100]={0};

This code using Linaro 4.8.3 calls the memset function which is creating a hard fault. I did set the stack pointer to the top of SRAM, and the program is very simple so stack should not be issue.

The NVIC_Fault_STAT has No Compressor Usage Fault Set.

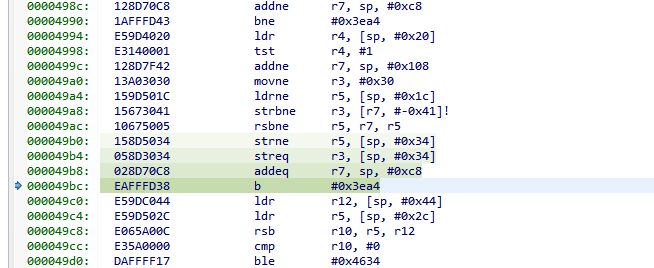

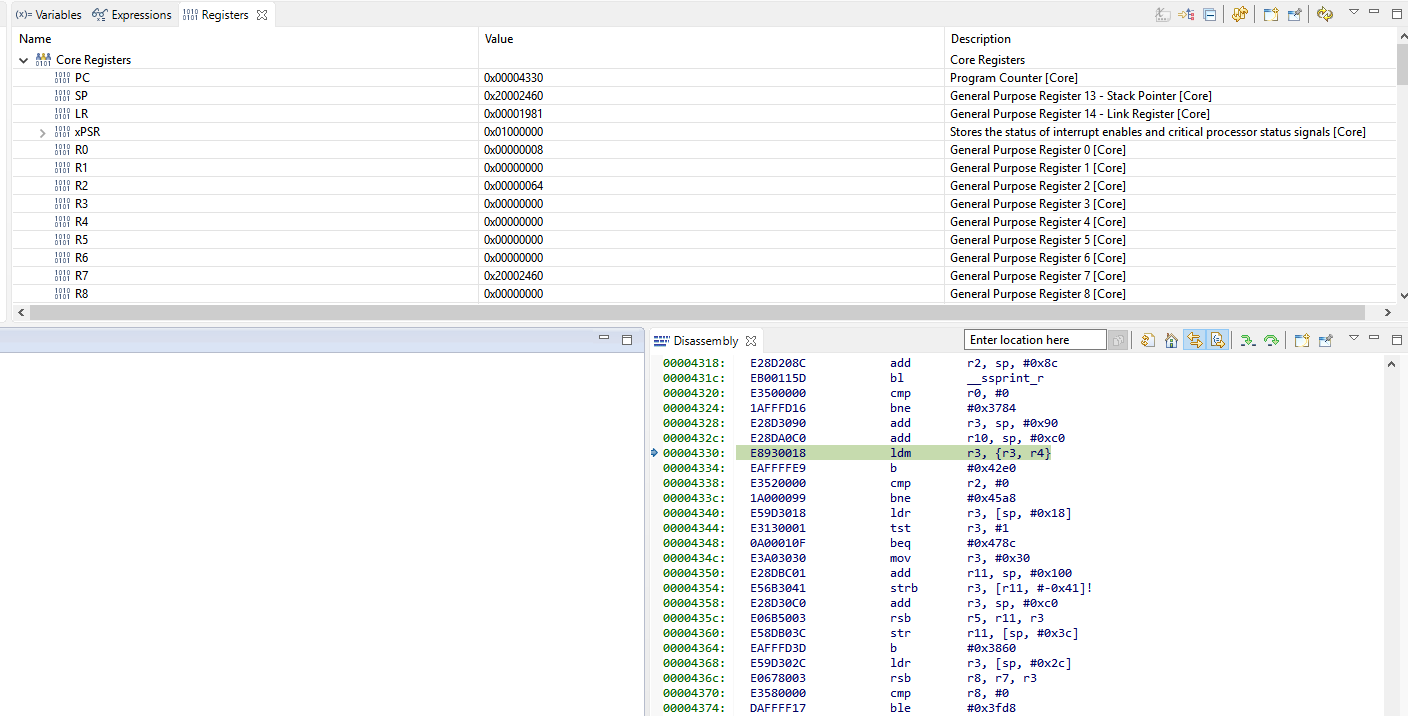

Below is the last instruction before the fault is set:

The code runs if compiled with the TI compiler, note I would use TI's compiler but at $750 for CCS I would just buy a chip from another vendor like Atmel.

I also tried the same code with Linaro 4.9.3 however it is getting stuck in the Default ISR Handler when executing code below, again in the memset.

Thanks

Trampas