Hi ,

In order to store specific string in certain offset in bin file , I have to modify the link file .

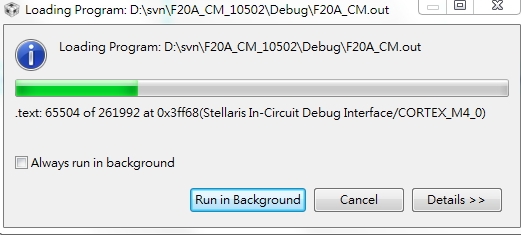

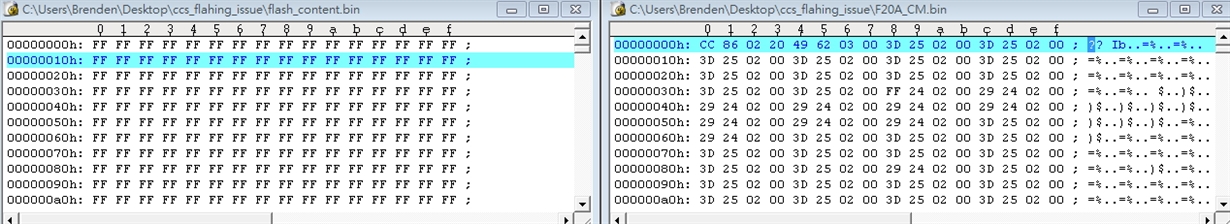

The Chip flash content is not equal to the bin file which build with modified link file loading with CCS .

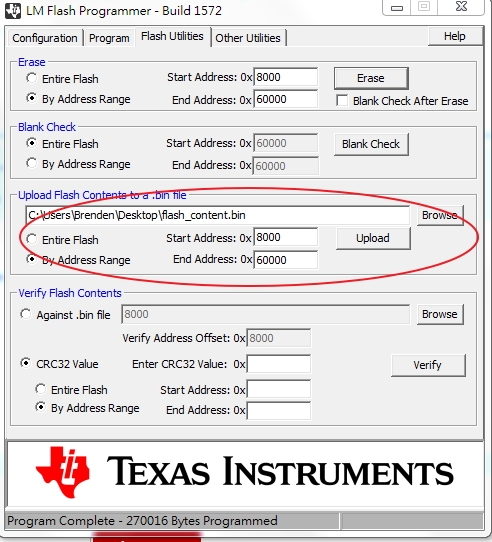

But i load the bin to chip flash with LMflash programer . The chip flash content is equal to the bin file .

Does it necessary to modify CCS project setting after modifying the link file ?

CCS version: CCS5.4.0.00091

Chip part number :Tiva TM4E129BNCZAD

link file content :

/******************************************************************************

*

* bmc_test_ccs.cmd - CCS linker configuration file for bmc_test.

*

* Copyright (c) 2013 Texas Instruments Incorporated. All rights reserved.

* Software License Agreement

*

* Texas Instruments (TI) is supplying this software for use solely and

* exclusively on TI's microcontroller products. The software is owned by

* TI and/or its suppliers, and is protected under applicable copyright

* laws. You may not combine this software with "viral" open-source

* software in order to form a larger program.

*

* THIS SOFTWARE IS PROVIDED "AS IS" AND WITH ALL FAULTS.

* NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT

* NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. TI SHALL NOT, UNDER ANY

* CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR CONSEQUENTIAL

* DAMAGES, FOR ANY REASON WHATSOEVER.

*

* This is part of revision 1235 of the DK-SMC-SNOWFLAKE Firmware Package.

*

* This is part of an ALPHA release.

* The software in this release is not intended for use in a production project.

*

*****************************************************************************/

--retain=g_pfnVectors

/* The following command line options are set as part of the CCS project. */

/* If you are building using the command line, or for some reason want to */

/* define them here, you can uncomment and modify these lines as needed. */

/* If you are using CCS for building, it is probably better to make any such */

/* modifications in your CCS project and leave this file alone. */

/* */

/* --heap_size=0 */

/* --stack_size=256 */

/* --library=rtsv7M3_T_le_eabi.lib */

/* The starting address of the application. Normally the interrupt vectors */

/* must be located at the beginning of the application. */

#define APP_BASE 0x00008000

#define RAM_BASE 0x20000000

/* System memory map */

MEMORY

{

/* Application stored in and executes from internal flash */

FLASH1 (RX) : origin = APP_BASE, length = 0x00001000 //store intvecs

FLASH2 (RX) : origin = APP_BASE+0x00001000, length = 0x00001000 //store fw check

FLASH3 (RX) : origin = APP_BASE+0x00002000, length = 0x00076000 // store others

FLASH4 (RX) : origin = 0x00080000, length = 0x00080000//no data section put here

/* Application uses internal RAM for data */

SRAM (RWX) : origin = 0x20000000, length = 0x00040000

}

/* Section allocation in memory */

SECTIONS

{

.intvecs: > APP_BASE

.fw_sect : > FLASH2

.text : > FLASH3

.const : > FLASH3

.cinit : > FLASH3

.pinit : > FLASH3

.init_array : > FLASH3

.vtable : > RAM_BASE

.data : > SRAM

.bss : > SRAM

.sysmem : > SRAM

.stack : > SRAM

}

__STACK_TOP = __stack + 512;

Brenden