Tool/software: Code Composer Studio

Hey.

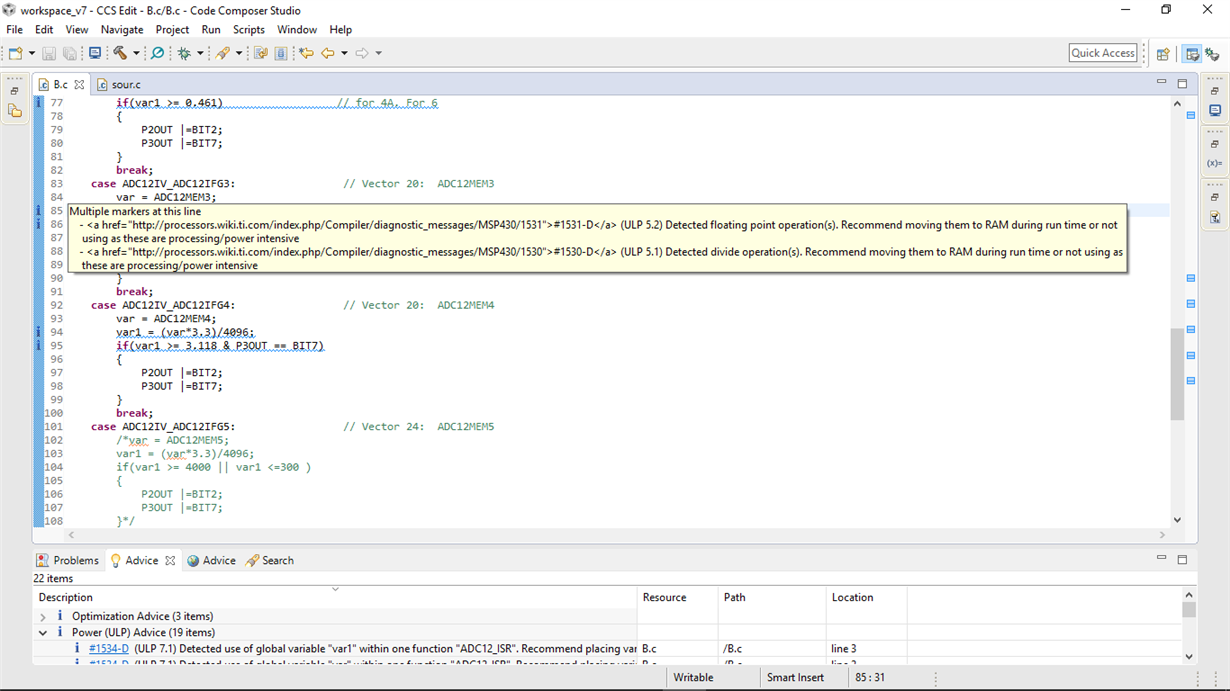

I am running a code and I get the following optimization advice.

Can someone tell me what the problem is and how to eliminate it?

#include <msp430.h>

static unsigned int var =0;

static unsigned int var1 =0;

void adcinit ()

{

ADC12CTL0 = ADC12SHT0_2 | ADC12ON | ADC12MSC; /* Sampling time, S&H=16, ADC12 on */

ADC12CTL1 = ADC12SHP | ADC12CONSEQ0 | ADC12CONSEQ1; /* Use sampling timer */

ADC12CTL2 |= ADC12RES_2; /* 12-bit conversion results */

ADC12MCTL0 |= ADC12INCH_0; /* A0 ADC input select; Vref=AVCC */

ADC12MCTL1 |= ADC12INCH_1; /* A1 ADC input select; Vref=AVCC */

ADC12MCTL2 |= ADC12INCH_2; /* A2 ADC input select; Vref=AVCC */

ADC12MCTL3 |= ADC12INCH_3; /* A3 ADC input select; Vref=AVCC */

ADC12MCTL4 |= ADC12INCH_4; /* A4 ADC input select; Vref=AVCC */

ADC12MCTL5 = ADC12INCH_6 | ADC12EOS ; /* A6 ADC input select; Vref=AVCC , End of sequence */

ADC12IER0 = ADC12IE0 | ADC12IE1 | ADC12IE2 | ADC12IE3 | ADC12IE4 | ADC12IE6 ; /* Enable ADC conv complete interrupt */

}

void clockinit()

{

/* operation beyond 8MHz _before_ configuring the clock system.*/

FRCTL0 = FRCTLPW | NWAITS_1;

// Clock System Setup

CSCTL0_H = CSKEY >> 8; /* Unlock CS registers*/

CSCTL1 = DCORSEL | DCOFSEL_4; /* Set DCO to 16MHz*/

CSCTL2 = SELA__VLOCLK | SELS__DCOCLK | SELM__DCOCLK; // Set SMCLK = MCLK = DCO,

/* ACLK = VLOCLK*/

CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; /* Set all dividers*/

CSCTL0_H = 0;

}

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

__bis_SR_register(GIE);

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

clockinit();

adcinit();

}

void __attribute__ ((interrupt(ADC12_VECTOR))) ADC12_ISR (void)

{

switch(__even_in_range(ADC12IV, ADC12IV_ADC12RDYIFG))

{

case ADC12IV_NONE: break; // Vector 0: No interrupt

case ADC12IV_ADC12OVIFG: break; // Vector 2: ADC12MEMx Overflow

case ADC12IV_ADC12TOVIFG: break; // Vector 4: Conversion time overflow

case ADC12IV_ADC12HIIFG: break; // Vector 6: ADC12BHI

case ADC12IV_ADC12LOIFG: break; // Vector 8: ADC12BLO

case ADC12IV_ADC12INIFG: break; // Vector 10: ADC12BIN

case ADC12IV_ADC12IFG0: // Vector 14: ADC12MEM0

var = ADC12MEM0;

var1 = (var*3.3)/4096;

if(var1 >= 1.82 || var1 <=1.64 )

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}

break;

case ADC12IV_ADC12IFG1: // Vector 14: ADC12MEM1

var = ADC12MEM1;

var1 = (var*3.3)/4096;

if(var1 >= 0.265)

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}

break;

case ADC12IV_ADC12IFG2: // Vector 18: ADC12MEM2

var = ADC12MEM2;

var1 = (var*3.3)/4096;

if(var1 >= 0.461) // for 4A. For 6

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}

break;

case ADC12IV_ADC12IFG3: // Vector 20: ADC12MEM3

var = ADC12MEM3;

var1 = (var*3.3)/4096;

if(var1 >= 3.121 & P2OUT == BIT2)

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}

break;

case ADC12IV_ADC12IFG4: // Vector 20: ADC12MEM4

var = ADC12MEM4;

var1 = (var*3.3)/4096;

if(var1 >= 3.118 & P3OUT == BIT7)

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}

break;

case ADC12IV_ADC12IFG5: // Vector 24: ADC12MEM5

/*var = ADC12MEM5;

var1 = (var*3.3)/4096;

if(var1 >= 4000 || var1 <=300 )

{

P2OUT |=BIT2;

P3OUT |=BIT7;

}*/

break;

case ADC12IV_ADC12IFG6: break; // Vector 24: ADC12MEM6

case ADC12IV_ADC12IFG7: break; // Vector 26: ADC12MEM7

case ADC12IV_ADC12IFG8: break; // Vector 28: ADC12MEM8

case ADC12IV_ADC12IFG9: break; // Vector 30: ADC12MEM9

case ADC12IV_ADC12IFG10: break; // Vector 32: ADC12MEM10

case ADC12IV_ADC12IFG11: break; // Vector 34: ADC12MEM11

case ADC12IV_ADC12IFG12: break; // Vector 36: ADC12MEM12

case ADC12IV_ADC12IFG13: break; // Vector 38: ADC12MEM13

case ADC12IV_ADC12IFG14: break; // Vector 40: ADC12MEM14

case ADC12IV_ADC12IFG15: break; // Vector 42: ADC12MEM15

case ADC12IV_ADC12IFG16: break; // Vector 44: ADC12MEM16

case ADC12IV_ADC12IFG17: break; // Vector 46: ADC12MEM17

case ADC12IV_ADC12IFG18: break; // Vector 48: ADC12MEM18

case ADC12IV_ADC12IFG19: break; // Vector 50: ADC12MEM19

case ADC12IV_ADC12IFG20: break; // Vector 52: ADC12MEM20

case ADC12IV_ADC12IFG21: break; // Vector 54: ADC12MEM21

case ADC12IV_ADC12IFG22: break; // Vector 56: ADC12MEM22

case ADC12IV_ADC12IFG23: break; // Vector 58: ADC12MEM23

case ADC12IV_ADC12IFG24: break; // Vector 60: ADC12MEM24

case ADC12IV_ADC12IFG25: break; // Vector 62: ADC12MEM25

case ADC12IV_ADC12IFG26: break; // Vector 64: ADC12MEM26

case ADC12IV_ADC12IFG27: break; // Vector 66: ADC12MEM27

case ADC12IV_ADC12IFG28: break; // Vector 68: ADC12MEM28

case ADC12IV_ADC12IFG29: break; // Vector 70: ADC12MEM29

case ADC12IV_ADC12IFG30: break; // Vector 72: ADC12MEM30

case ADC12IV_ADC12IFG31: break; // Vector 74: ADC12MEM31

case ADC12IV_ADC12RDYIFG: break; // Vector 76: ADC12RDY

default: break;

}

}

Given above is the full code.

Thank you in advance.

Viswanath.