Part Number: TMS320F28031

Tool/software: Code Composer Studio

Hi,

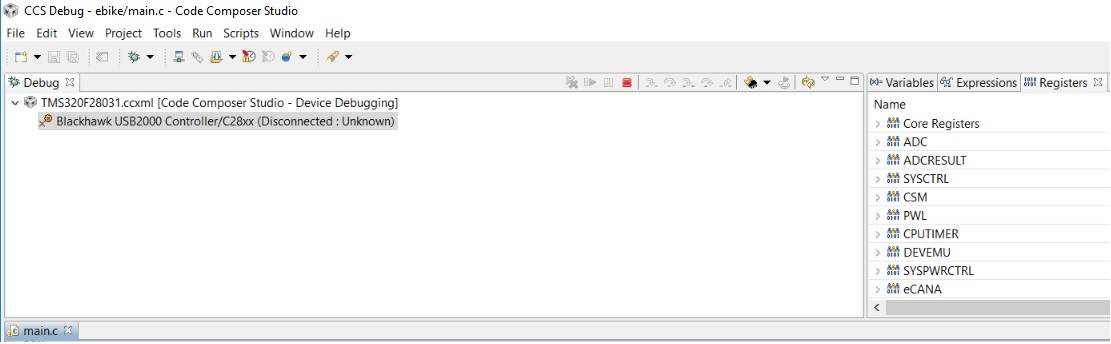

I am trying to use BlackHawk USB2000 emulator to debug the code on processor (28031) having issues in launching the debug session. It does pass the communication test and when I try to launch the debug session the code composer just hangs there and stays there in launching point for hours and hours.

I am using Code composer studio 5.5.0.00077 and BlackHawk USB 2000 controller (BH-USB-2000). I have also tried uninstalling the code composer studio and fresh installation with fresh workspace but still same result.

Any help is appreciated.

Thanks