Other Parts Discussed in Thread: MOTORWARE, CONTROLSUITE, TMS320F28054M

Tool/software: Code Composer Studio

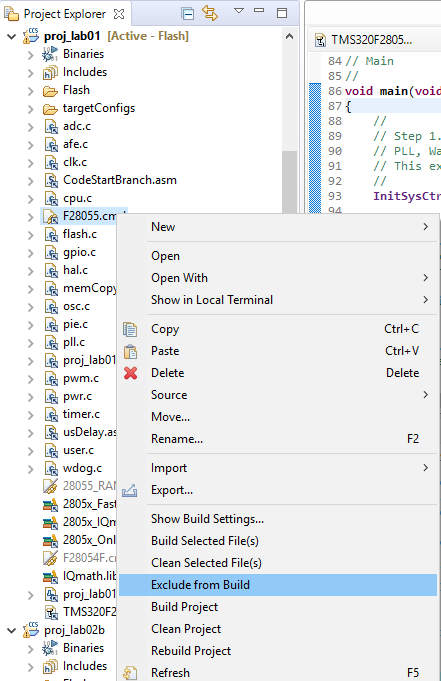

after uninstalling CCS, Motorware, Control Suite and deleting the TI directory and the project workspace then reinstalling CCS8.1.0.00011_win32, controlSUITE3.4.9 and motorware_1_01_00_18 for a clean install I went to C:\ti\motorware\motorware_1_01_00_18\sw\solutions\instaspin_foc\boards\hvkit_rev1p1\f28x\f2805xF\projects\ccs\proj_lab01 and opened the project. first thing I noticed is the wrong build command - it's trying to use make. I close CCS and reopen and magically the correct build command shows up.

but the worst part is if I change anything in Properties/Project for example setting the correct Variant and the correct device the configuration goes way off track, no longer can I build with the F28054F.cmd file I need to flash, even if I set it there the config changes after I close it, I can't build correctly and I can't recover, hense the uninstalling, deleting etc to get a clean install. using the manual project configuration somethings works but quickly goes down the tubes. I have quite a bit of experience in the field and I've never had this kind of experience with an eclipse based IDE. this is unusable as it is and trying to figure out how to make it work has taken a lot of time.

Maybe it's possible I'm doing something unexpected but I don't think so. Maybe the security software is doing something. Maybe I won't recommend using TI chips anymore.

I called the only tech line I could find but that was a training line, the person there gave me a 1-800 number and patched me through, that number said the number had changed and to call this other number. I called the other number and before I even explained the problem I was put on hold. Is this how TI cares?

I need to talk with someone that understands what's going on so I can get past not being able to build code for a TI product with a TI IDE.