Part Number: EVMK2G

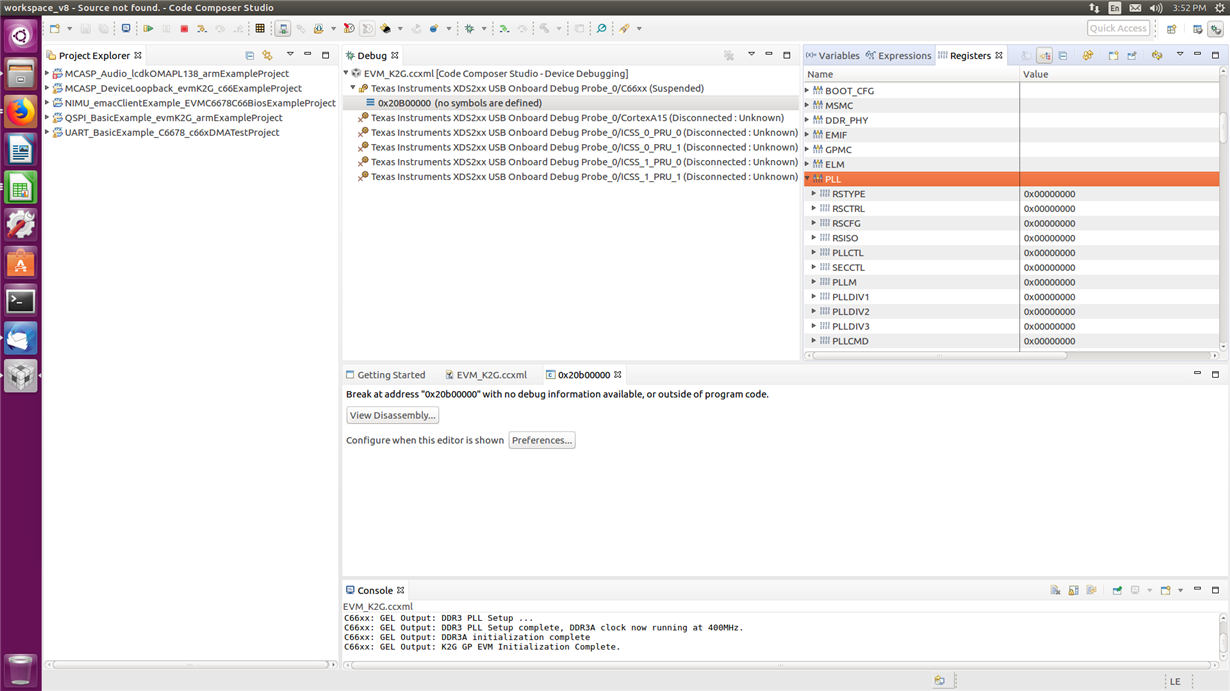

Tool/software: Code Composer Studio

Hi,

I'm trying to write to the SPI registers but get a "data abort" error, looking at the register window in CCS debug, while most register groups are readable, the SPI register group shows "error: unable to read" by each register. I must be missing a step in enabling the SPI, please could you let me know what I need to be doing at startup?

Thanks,

Steve