Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

Tool/software: Code Composer Studio

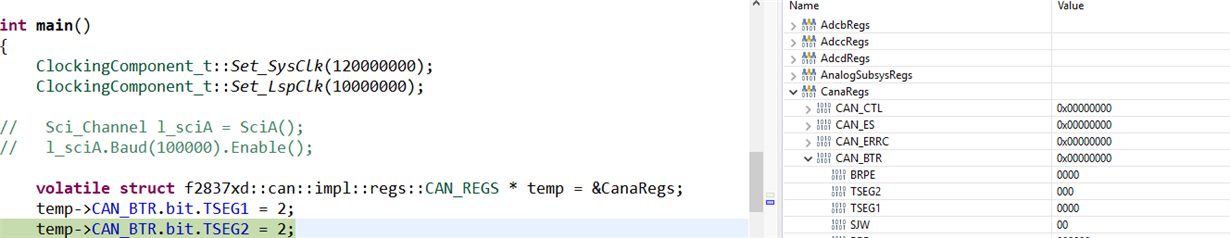

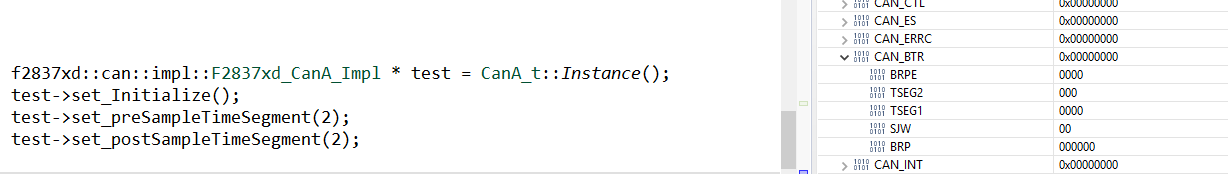

When debugging our LaunchXL-F2379D through the onboard XDS100we cannot see registers associated with a hardware peripheral, though the data pointers can be seen pointing to the correct addresses in memory to do so. This only occurs within implementations where we utilize CAN, and is isolated to this module as well. Similar operations on other peripherals like SCI and CPU Timers yields expected behavior. With the CAN register sets, however, not only are reads unavailable to us within the debugger view (seen in the picture below, reads to the pointer 'm_Reg' at the lowest level return an error), we also cannot seem to update the registers from compiled instruction sets as we watch them in real time from within the register window. As we make direct writes to the pointer 'm_Reg' mentioned above, the values are not reflected as they should be within the hardware registers. I have included our linker command file as well.

Attempting to look at the registers through our variable window is the best clue that we've been able to find so far. Expanding the data pointer which is meant to point at the register its wrapper class is named after tells us that the "memory map prevented reading address ... " though looking at the pointer itself, we see that it is indeed pointing at the location it is meant to. The CAN register section is separate from the other peripherals in location and function, so I think that we are missing some rule or statement that configures either the compiled code or the debugger to read them correctly.

The memory sections defined there map to the correct locations for this microprocessor, and our source code references those sections using "#pragma DATA_SECTION()". I have included the linker file and our register definition file, they are the default C2000Ware provided versions with some modifications made. I am not able to provide source code, but if there is any other forms of data that would be helpful then I am happy to provide them.

MEMORY

{

PAGE 0 : /* Program Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE1 for data allocation */

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x000122, length = 0x0002DE

RAMD0 : origin = 0x00B000, length = 0x000800

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMGS14 : origin = 0x01A000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS15 : origin = 0x01B000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

FLASHA : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

/*FLASHB : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASHBC : origin = 0x082000, length = 0x004000 /* on-chip Flash */

FLASHD : origin = 0x086000, length = 0x002000 /* on-chip Flash */

/*FLASHE : origin = 0x088000, length = 0x008000 /* on-chip Flash */

/*FLASHF : origin = 0x090000, length = 0x008000 /* on-chip Flash */

/*FLASHG : origin = 0x098000, length = 0x008000 /* on-chip Flash */

/*FLASHH : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

/*FLASHI : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASHEFGHIJ : origin = 0x088000, length = 0x030000 /* on-chip Flash */

/*FLASHK : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

/*FLASHL : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

/*FLASHM : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASHKLMN : origin = 0x0B8000, length = 0x008000 /* on-chip Flash */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH) blocks can be moved to PAGE0 for program allocation */

BOOT_RSVD : origin = 0x000002, length = 0x000120 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAMD1 : origin = 0x00B800, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x001000

RAMGS1 : origin = 0x00D000, length = 0x001000

RAMGS2 : origin = 0x00E000, length = 0x001000

RAMGS3 : origin = 0x00F000, length = 0x001000

RAMGS4 : origin = 0x010000, length = 0x001000

/*RAMGS5 : origin = 0x011000, length = 0x001000

RAMGS6 : origin = 0x012000, length = 0x001000

RAMGS7 : origin = 0x013000, length = 0x001000

RAMGS8 : origin = 0x014000, length = 0x001000*/

RAMGS56789 : origin = 0x011000, length = 0x005000

RAMGS10 : origin = 0x016000, length = 0x001000

RAMGS11 : origin = 0x017000, length = 0x001000

RAMGS12 : origin = 0x018000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

RAMGS13 : origin = 0x019000, length = 0x001000 /* Only Available on F28379D, F28377D, F28375D devices. Remove line on other devices. */

CPU2TOCPU1RAM : origin = 0x03F800, length = 0x000400

CPU1TOCPU2RAM : origin = 0x03FC00, length = 0x000400

ADCA_RESULT : origin = 0x000B00, length = 0x000020

ADCB_RESULT : origin = 0x000B20, length = 0x000020

ADCC_RESULT : origin = 0x000B40, length = 0x000020

ADCD_RESULT : origin = 0x000B60, length = 0x000020

ADCA : origin = 0x007400, length = 0x000080

ADCB : origin = 0x007480, length = 0x000080

ADCC : origin = 0x007500, length = 0x000080

ADCD : origin = 0x007580, length = 0x000080

ANALOG_SUBSYS : origin = 0x05D180, length = 0x000080

CANA : origin = 0x048000, length = 0x000800

CANB : origin = 0x04A000, length = 0x000800

CLA1 : origin = 0x001400, length = 0x000040 /* CLA registers */

CLB_XBAR : origin = 0x007A40, length = 0x000040

CMPSS1 : origin = 0x005C80, length = 0x000020

CMPSS2 : origin = 0x005CA0, length = 0x000020

CMPSS3 : origin = 0x005CC0, length = 0x000020

CMPSS4 : origin = 0x005CE0, length = 0x000020

CMPSS5 : origin = 0x005D00, length = 0x000020

CMPSS6 : origin = 0x005D20, length = 0x000020

CMPSS7 : origin = 0x005D40, length = 0x000020

CMPSS8 : origin = 0x005D60, length = 0x000020

CPU_TIMER0 : origin = 0x000C00, length = 0x000008 /* CPU Timer0 registers */

CPU_TIMER1 : origin = 0x000C08, length = 0x000008 /* CPU Timer1 registers */

CPU_TIMER2 : origin = 0x000C10, length = 0x000008 /* CPU Timer2 registers */

DACA : origin = 0x005C00, length = 0x000010

DACB : origin = 0x005C10, length = 0x000010

DACC : origin = 0x005C20, length = 0x000010

DMA : origin = 0x001000, length = 0x000200

DMACLASRCSEL : origin = 0x007980, length = 0x000040

ECAP1 : origin = 0x005000, length = 0x000020 /* Enhanced Capture 1 registers */

ECAP2 : origin = 0x005020, length = 0x000020 /* Enhanced Capture 2 registers */

ECAP3 : origin = 0x005040, length = 0x000020 /* Enhanced Capture 3 registers */

ECAP4 : origin = 0x005060, length = 0x000020 /* Enhanced Capture 4 registers */

ECAP5 : origin = 0x005080, length = 0x000020 /* Enhanced Capture 5 registers */

ECAP6 : origin = 0x0050A0, length = 0x000020 /* Enhanced Capture 6 registers */

EMIF1 : origin = 0x047000, length = 0x000800

EMIF2 : origin = 0x047800, length = 0x000800

EQEP1 : origin = 0x005100, length = 0x000040 /* Enhanced QEP 1 registers */

EQEP2 : origin = 0x005140, length = 0x000040 /* Enhanced QEP 2 registers */

EQEP3 : origin = 0x005180, length = 0x000040 /* Enhanced QEP 3 registers */

EPWM1 : origin = 0x004000, length = 0x000100 /* Enhanced PWM 1 registers */

EPWM2 : origin = 0x004100, length = 0x000100 /* Enhanced PWM 2 registers */

EPWM3 : origin = 0x004200, length = 0x000100 /* Enhanced PWM 3 registers */

EPWM4 : origin = 0x004300, length = 0x000100 /* Enhanced PWM 4 registers */

EPWM5 : origin = 0x004400, length = 0x000100 /* Enhanced PWM 5 registers */

EPWM6 : origin = 0x004500, length = 0x000100 /* Enhanced PWM 6 registers */

EPWM7 : origin = 0x004600, length = 0x000100 /* Enhanced PWM 7 registers */

EPWM8 : origin = 0x004700, length = 0x000100 /* Enhanced PWM 8 registers */

EPWM9 : origin = 0x004800, length = 0x000100 /* Enhanced PWM 9 registers */

EPWM10 : origin = 0x004900, length = 0x000100 /* Enhanced PWM 10 registers */

EPWM11 : origin = 0x004A00, length = 0x000100 /* Enhanced PWM 11 registers */

EPWM12 : origin = 0x004B00, length = 0x000100 /* Enhanced PWM 12 registers */

EPWM_XBAR : origin = 0x007A00, length = 0x000040

FLASH0_CTRL : origin = 0x05F800, length = 0x000300

FLASH0_ECC : origin = 0x05FB00, length = 0x000040

GPIOCTRL : origin = 0x007C00, length = 0x000180 /* GPIO control registers */

GPIODAT : origin = 0x007F00, length = 0x000030 /* GPIO data registers */

OUTPUT_XBAR : origin = 0x007A80, length = 0x000040

I2CA : origin = 0x007300, length = 0x000040 /* I2C-A registers */

I2CB : origin = 0x007340, length = 0x000040 /* I2C-B registers */

IPC : origin = 0x050000, length = 0x000024

FLASHPUMPSEMAPHORE : origin = 0x050024, length = 0x000002

ROMPREFETCH : origin = 0x05E608, length = 0x000002

MEMCFG : origin = 0x05F400, length = 0x000080 /* Mem Config registers */

EMIF1CONFIG : origin = 0x05F480, length = 0x000020 /* Emif-1 Config registers */

EMIF2CONFIG : origin = 0x05F4A0, length = 0x000020 /* Emif-2 Config registers */

ACCESSPROTECTION : origin = 0x05F4C0, length = 0x000040 /* Access Protection registers */

MEMORYERROR : origin = 0x05F500, length = 0x000040 /* Access Protection registers */

ROMWAITSTATE : origin = 0x05F540, length = 0x000002 /* ROM Config registers */

MCBSPA : origin = 0x006000, length = 0x000040 /* McBSP-A registers */

MCBSPB : origin = 0x006040, length = 0x000040 /* McBSP-A registers */

NMIINTRUPT : origin = 0x007060, length = 0x000010 /* NMI Watchdog Interrupt Registers */

PIE_CTRL : origin = 0x000CE0, length = 0x000020 /* PIE control registers */

PIE_VECT : origin = 0x000D00, length = 0x000200 /* PIE Vector Table */

SCIA : origin = 0x007200, length = 0x000010 /* SCI-A registers */

SCIB : origin = 0x007210, length = 0x000010 /* SCI-B registers */

SCIC : origin = 0x007220, length = 0x000010 /* SCI-C registers */

SCID : origin = 0x007230, length = 0x000010 /* SCI-D registers */

SDFM1 : origin = 0x005E00, length = 0x000080 /* Sigma delta 1 registers */

SDFM2 : origin = 0x005E80, length = 0x000080 /* Sigma delta 2 registers */

SPIA : origin = 0x006100, length = 0x000010

SPIB : origin = 0x006110, length = 0x000010

SPIC : origin = 0x006120, length = 0x000010

SPID : origin = 0x006130, length = 0x000010

UPP : origin = 0x006200, length = 0x000100 /* uPP registers */

DEV_CFG : origin = 0x05D000, length = 0x000180

CLK_CFG : origin = 0x05D200, length = 0x000100

CPU_SYS : origin = 0x05D300, length = 0x000100

INPUT_XBAR : origin = 0x007900, length = 0x000020

XBAR : origin = 0x007920, length = 0x000020

SYNC_SOC : origin = 0x007940, length = 0x000010

WD : origin = 0x007000, length = 0x000040

XINT : origin = 0x007070, length = 0x000010

DCSM_Z1 : origin = 0x05F000, length = 0x000030 /* Zone 1 Dual code security module registers */

DCSM_Z2 : origin = 0x05F040, length = 0x000030 /* Zone 2 Dual code security module registers */

DCSM_COMMON : origin = 0x05F070, length = 0x000010 /* Common Dual code security module registers */

}

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHBC, PAGE = 0, ALIGN(4)

.pinit : > FLASHBC, PAGE = 0, ALIGN(4)

.text : >> FLASHEFGHIJ | FLASHKLMN PAGE = 0, ALIGN(4)

codestart : > BEGIN, PAGE = 0, ALIGN(4)

/* Allocate uninitalized data sections: */

.stack : > RAMD1, PAGE = 1

.ebss : > RAMGS56789, PAGE = 1

.esysmem : > RAMGS3, PAGE = 1

.cio : >> RAMGS3 | RAMGS4 PAGE = 1

/* Initalized sections go in Flash */

.econst : > FLASHKLMN, PAGE = 0, ALIGN(4)

.switch : > FLASHKLMN, PAGE = 0, ALIGN(4)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

Filter_RegsFile : > RAMGS0, PAGE = 1

SHARERAMGS0 : > RAMGS0, PAGE = 1

SHARERAMGS1 : > RAMGS1, PAGE = 1

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

UNION run = PIE_VECT, PAGE = 1

{

PieVectTableFile

GROUP

{

EmuBModeVar

EmuBootPinsVar

}

}

AdcaResultFile : > ADCA_RESULT, PAGE = 1

AdcbResultFile : > ADCB_RESULT, PAGE = 1

AdccResultFile : > ADCC_RESULT, PAGE = 1

AdcdResultFile : > ADCD_RESULT, PAGE = 1

AdcaRegsFile : > ADCA, PAGE = 1

AdcbRegsFile : > ADCB, PAGE = 1

AdccRegsFile : > ADCC, PAGE = 1

AdcdRegsFile : > ADCD, PAGE = 1

AnalogSubsysRegsFile : > ANALOG_SUBSYS, PAGE = 1

CanaRegsFile : > CANA, PAGE = 1

CanbRegsFile : > CANB, PAGE = 1

Cla1RegsFile : > CLA1, PAGE = 1

Cla1SoftIntRegsFile : > PIE_CTRL, PAGE = 1, type=DSECT

ClbXbarRegsFile : > CLB_XBAR PAGE = 1

Cmpss1RegsFile : > CMPSS1, PAGE = 1

Cmpss2RegsFile : > CMPSS2, PAGE = 1

Cmpss3RegsFile : > CMPSS3, PAGE = 1

Cmpss4RegsFile : > CMPSS4, PAGE = 1

Cmpss5RegsFile : > CMPSS5, PAGE = 1

Cmpss6RegsFile : > CMPSS6, PAGE = 1

Cmpss7RegsFile : > CMPSS7, PAGE = 1

Cmpss8RegsFile : > CMPSS8, PAGE = 1

CpuTimer0RegsFile : > CPU_TIMER0, PAGE = 1

CpuTimer1RegsFile : > CPU_TIMER1, PAGE = 1

CpuTimer2RegsFile : > CPU_TIMER2, PAGE = 1

DacaRegsFile : > DACA PAGE = 1

DacbRegsFile : > DACB PAGE = 1

DaccRegsFile : > DACC PAGE = 1

DcsmZ1RegsFile : > DCSM_Z1, PAGE = 1

DcsmZ2RegsFile : > DCSM_Z2, PAGE = 1

DcsmCommonRegsFile : > DCSM_COMMON, PAGE = 1

DmaRegsFile : > DMA PAGE = 1

DmaClaSrcSelRegsFile : > DMACLASRCSEL PAGE = 1

ECap1RegsFile : > ECAP1, PAGE = 1

ECap2RegsFile : > ECAP2, PAGE = 1

ECap3RegsFile : > ECAP3, PAGE = 1

ECap4RegsFile : > ECAP4, PAGE = 1

ECap5RegsFile : > ECAP5, PAGE = 1

ECap6RegsFile : > ECAP6, PAGE = 1

Emif1RegsFile : > EMIF1 PAGE = 1

Emif2RegsFile : > EMIF2 PAGE = 1

EPwm1RegsFile : > EPWM1, PAGE = 1

EPwm2RegsFile : > EPWM2, PAGE = 1

EPwm3RegsFile : > EPWM3, PAGE = 1

EPwm4RegsFile : > EPWM4, PAGE = 1

EPwm5RegsFile : > EPWM5, PAGE = 1

EPwm6RegsFile : > EPWM6, PAGE = 1

EPwm7RegsFile : > EPWM7, PAGE = 1

EPwm8RegsFile : > EPWM8, PAGE = 1

EPwm9RegsFile : > EPWM9, PAGE = 1

EPwm10RegsFile : > EPWM10, PAGE = 1

EPwm11RegsFile : > EPWM11, PAGE = 1

EPwm12RegsFile : > EPWM12, PAGE = 1

EPwmXbarRegsFile : > EPWM_XBAR PAGE = 1

EQep1RegsFile : > EQEP1, PAGE = 1

EQep2RegsFile : > EQEP2, PAGE = 1

EQep3RegsFile : > EQEP3, PAGE = 1

Flash0CtrlRegsFile : > FLASH0_CTRL PAGE = 1

Flash0EccRegsFile : > FLASH0_ECC PAGE = 1

GpioCtrlRegsFile : > GPIOCTRL, PAGE = 1

GpioDataRegsFile : > GPIODAT, PAGE = 1

OutputXbarRegsFile : > OUTPUT_XBAR PAGE = 1

I2caRegsFile : > I2CA, PAGE = 1

I2cbRegsFile : > I2CB, PAGE = 1

InputXbarRegsFile : > INPUT_XBAR PAGE = 1

XbarRegsFile : > XBAR PAGE = 1

IpcRegsFile : > IPC, PAGE = 1

FlashPumpSemaphoreRegsFile : > FLASHPUMPSEMAPHORE, PAGE = 1

RomPrefetchRegsFile : > ROMPREFETCH, PAGE = 1

MemCfgRegsFile : > MEMCFG, PAGE = 1

Emif1ConfigRegsFile : > EMIF1CONFIG, PAGE = 1

Emif2ConfigRegsFile : > EMIF2CONFIG, PAGE = 1

AccessProtectionRegsFile : > ACCESSPROTECTION, PAGE = 1

MemoryErrorRegsFile : > MEMORYERROR, PAGE = 1

RomWaitStateRegsFile : > ROMWAITSTATE, PAGE = 1

McbspaRegsFile : > MCBSPA, PAGE = 1

McbspbRegsFile : > MCBSPB, PAGE = 1

UppRegsFile : > UPP, PAGE = 1

NmiIntruptRegsFile : > NMIINTRUPT, PAGE = 1

PieCtrlRegsFile : > PIE_CTRL, PAGE = 1

SciaRegsFile : > SCIA, PAGE = 1

ScibRegsFile : > SCIB, PAGE = 1

ScicRegsFile : > SCIC, PAGE = 1

ScidRegsFile : > SCID, PAGE = 1

Sdfm1RegsFile : > SDFM1, PAGE = 1

Sdfm2RegsFile : > SDFM2, PAGE = 1

SpiaRegsFile : > SPIA, PAGE = 1

SpibRegsFile : > SPIB, PAGE = 1

SpicRegsFile : > SPIC, PAGE = 1

SpidRegsFile : > SPID, PAGE = 1

DevCfgRegsFile : > DEV_CFG, PAGE = 1

ClkCfgRegsFile : > CLK_CFG, PAGE = 1

CpuSysRegsFile : > CPU_SYS, PAGE = 1

SyncSocRegsFile : > SYNC_SOC, PAGE = 1

WdRegsFile : > WD, PAGE = 1

XintRegsFile : > XINT PAGE = 1

MemCfgRegs : > MEMCFG PAGE = 1

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 15009000

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS0 | RAMLS1 | RAMLS2 |RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#else

ramfuncs : LOAD = FLASHD,

RUN = RAMLS0 | RAMLS1 | RAMLS2 |RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#endif

#endif

/* The following section definitions are required when using the IPC API Drivers */

GROUP : > CPU1TOCPU2RAM, PAGE = 1

{

PUTBUFFER

PUTWRITEIDX

GETREADIDX

}

GROUP : > CPU2TOCPU1RAM, PAGE = 1

{

GETBUFFER : TYPE = DSECT

GETWRITEIDX : TYPE = DSECT

PUTREADIDX : TYPE = DSECT

}

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

/*

* Can_Regs.hpp

*

* Created on: Mar 19, 2020

* Author: chaparrojd

*/

#ifndef INCLUDE_F2837XD_CAN_IMPLEMENTATION_CAN_REGS_HPP_

#define INCLUDE_F2837XD_CAN_IMPLEMENTATION_CAN_REGS_HPP_

#include <Interface/Platform_Defines.hpp>

//#include <Source/Common/Regs/F2837xd_Can_Regs.hpp>

namespace f2837xd

{

namespace can

{

namespace impl

{

namespace regs

{

extern "C"

{

struct CAN_CTL_BITS

{

bp_16 Init:1; ///> 0 Initialization

bp_16 IE0:1; ///> 1 Interrupt line 0 Enable

bp_16 SIE:1; ///> 2 Status Change Interrupt Enable

bp_16 EIE:1; ///> 3 Error Interrupt Enable

bp_16 rsvd1:1; ///> 4 Reserved

bp_16 DAR:1; ///> 5 Disable Automatic Retransmission

bp_16 CCE:1; ///> 6 Configuration Change Enable

bp_16 Test:1; ///> 7 Test Mode Enable

bp_16 IDS:1; ///> 8 Interruption Debug Support Enable

bp_16 ABO:1; ///> 9 Auto-Bus-On Enable

bp_16 PMD:4; ///> 13:10 Parity on/off

bp_16 rsvd2:1; ///> 14 Reserved

bp_16 SWR:1; ///> 15 SW Reset Enable

bp_32 INITDBG:1; ///> 16 Debug Mode Status

bp_32 IE1:1; ///> 17 Interrupt line 1 Enable Disabled

bp_32 rsvd3:1; ///> 18 Reserved

bp_32 rsvd4:1; ///> 19 Reserved

bp_32 rsvd5:1; ///> 20 Reserved

bp_32 rsvd6:3; ///> 23:21 Reserved

bp_32 rsvd7:1; ///> 24 Reserved

bp_32 rsvd8:1; ///> 25 Reserved

bp_32 rsvd9:6; ///> 31:26 Reserved

};

union CAN_CTL_REG

{

bp_32 all;

struct CAN_CTL_BITS bit;

};

struct CAN_ES_BITS

{

bp_16 LEC:3; ///> 2:0 Last Error Code

bp_16 TxOk:1; ///> 3 Transmission status

bp_16 RxOk:1; ///> 4 Reception status

bp_16 EPass:1; ///> 5 Error Passive State

bp_16 EWarn:1; ///> 6 Warning State

bp_16 BOff:1; ///> 7 Bus-Off State

bp_16 PER:1; ///> 8 Parity Error Detected

bp_16 rsvd1:1; ///> 9 Reserved

bp_16 rsvd2:1; ///> 10 Reserved

bp_16 rsvd3:5; ///> 15:11 Reserved

bp_32 rsvd4:16; ///> 31:16 Reserved

};

union CAN_ES_REG

{

bp_32 all;

struct CAN_ES_BITS bit;

};

struct CAN_ERRC_BITS

{

bp_16 TEC:8; ///> 7:0 Transmit Error Counter

bp_16 REC:7; ///> 14:8 Receive Error Counter

bp_16 RP:1; ///> 15 Receive Error Passive

bp_32 rsvd1:16; ///> 31:16 Reserved

};

union CAN_ERRC_REG

{

bp_32 all;

struct CAN_ERRC_BITS bit;

};

struct CAN_BTR_BITS

{

bp_16 BRP:6; ///> 5:0 Baud Rate Prescaler

bp_16 SJW:2; ///> 7:6 Synchronization Jump Width

bp_16 TSEG1:4; ///> 11:8 Time segment

bp_16 TSEG2:3; ///> 14:12 Time segment

bp_16 rsvd1:1; ///> 15 Reserved

bp_32 BRPE:4; ///> 19:16 Baud Rate Prescaler Extension

bp_32 rsvd2:12; ///> 31:20 Reserved

};

union CAN_BTR_REG

{

bp_32 all;

struct CAN_BTR_BITS bit;

};

struct CAN_INT_BITS

{

bp_16 INT0ID:16; ///> 15:0 Interrupt Identifier

bp_32 INT1ID:8; ///> 23:16 Interrupt 1 Identifier

bp_32 rsvd1:8; ///> 31:24 Reserved

};

union CAN_INT_REG

{

bp_32 all;

struct CAN_INT_BITS bit;

};

struct CAN_TEST_BITS

{

bp_16 rsvd1:3; ///> 2:0 Reserved

bp_16 SILENT:1; ///> 3 Silent Mode

bp_16 LBACK:1; ///> 4 Loopback Mode

bp_16 TX:2; ///> 6:5 CANTX Pin Control

bp_16 RX:1; ///> 7 CANRX Pin Status

bp_16 EXL:1; ///> 8 External Loopback Mode

bp_16 RDA:1; ///> 9 RAM Direct Access Enable:

bp_16 rsvd2:6; ///> 15:10 Reserved

bp_32 rsvd3:16; ///> 31:16 Reserved

};

union CAN_TEST_REG

{

bp_32 all;

struct CAN_TEST_BITS bit;

};

struct CAN_PERR_BITS

{

bp_16 MSG_NUM:8; ///> 7:0 Message Number

bp_16 WORD_NUM:3; ///> 10:8 Word Number

bp_16 rsvd1:5; ///> 15:11 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_PERR_REG

{

bp_32 all;

struct CAN_PERR_BITS bit;

};

struct CAN_RAM_INIT_BITS

{

bp_16 KEY0:1; ///> 0 KEY0

bp_16 KEY1:1; ///> 1 KEY1

bp_16 KEY2:1; ///> 2 KEY2

bp_16 KEY3:1; ///> 3 KEY3

bp_16 CAN_RAM_INIT:1; ///> 4 Initialize CAN Mailbox RAM

bp_16 RAM_INIT_DONE:1; ///> 5 CAN RAM initialization complete

bp_16 rsvd1:10; ///> 15:6 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_RAM_INIT_REG

{

bp_32 all;

struct CAN_RAM_INIT_BITS bit;

};

struct CAN_GLB_INT_EN_BITS

{

bp_16 GLBINT0_EN:1; ///> 0 Global Interrupt Enable for CAN INT0

bp_16 GLBINT1_EN:1; ///> 1 Global Interrupt Enable for CAN INT1

bp_16 rsvd1:14; ///> 15:2 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_GLB_INT_EN_REG

{

bp_32 all;

struct CAN_GLB_INT_EN_BITS bit;

};

struct CAN_GLB_INT_FLG_BITS

{

bp_16 INT0_FLG:1; ///> 0 Global Interrupt Flag for CAN INT0

bp_16 INT1_FLG:1; ///> 1 Global Interrupt Flag for CAN INT1

bp_16 rsvd1:14; ///> 15:2 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_GLB_INT_FLG_REG

{

bp_32 all;

struct CAN_GLB_INT_FLG_BITS bit;

};

struct CAN_GLB_INT_CLR_BITS

{

bp_16 INT0_FLG_CLR:1; ///> 0 Global Interrupt flag clear for CAN INT0

bp_16 INT1_FLG_CLR:1; ///> 1 Global Interrupt flag clear for CAN INT1

bp_16 rsvd1:14; ///> 15:2 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_GLB_INT_CLR_REG

{

bp_32 all;

struct CAN_GLB_INT_CLR_BITS bit;

};

struct CAN_ABOTR_BITS

{

bp_32 abotr:32;

};

union CAN_ABOTR_REG

{

bp_32 all;

struct CAN_ABOTR_BITS bit;

};

struct CAN_TXRQ_X_BITS

{

bp_16 TxRqstReg1:2; ///> 1:0 Transmit Request Register 1

bp_16 TxRqstReg2:2; ///> 3:2 Transmit Request Register 2

bp_16 rsvd1:12; ///> 15:4 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_TXRQ_X_REG

{

bp_32 all;

struct CAN_TXRQ_X_BITS bit;

};

struct CAN_TXRQ_21_BITS

{

bp_32 TxRqst:32; ///> 31:16 Reserved

};

union CAN_TXRQ_21_REG

{

bp_32 all;

struct CAN_TXRQ_21_BITS bit;

};

struct CAN_NDAT_X_BITS

{

bp_16 NewDatReg1:2; ///> 1:0 New Data Register 1

bp_16 NewDatReg2:2; ///> 3:2 New Data Register 2

bp_16 rsvd1:12; ///> 15:4 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_NDAT_X_REG

{

bp_32 all;

struct CAN_NDAT_X_BITS bit;

};

struct CAN_NDAT_21_BITS

{

bp_32 NewDat:32; ///> 1:0 New Data Register 1

};

union CAN_NDAT_21_REG

{

bp_32 all;

struct CAN_NDAT_21_BITS bit;

};

struct CAN_IPEN_X_BITS

{

bp_16 IntPndReg1:2; ///> 1:0 Interrupt Pending Register 1

bp_16 IntPndReg2:2; ///> 3:2 Interrupt Pending Register 2

bp_16 rsvd1:12; ///> 15:4 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_IPEN_X_REG

{

bp_32 all;

struct CAN_IPEN_X_BITS bit;

};

struct CAN_IPEN_21_BITS

{

bp_32 IntPnd:32; ///> 1:0 Interrupt Pending Register 1

};

union CAN_IPEN_21_REG

{

bp_32 all;

struct CAN_IPEN_21_BITS bit;

};

struct CAN_MVAL_X_BITS

{

bp_16 MsgValReg1:2; ///> 1:0 Message Valid Register 1

bp_16 MsgValReg2:2; ///> 3:2 Message Valid Register 2

bp_16 rsvd1:12; ///> 15:4 Reserved

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_MVAL_X_REG

{

bp_32 all;

struct CAN_MVAL_X_BITS bit;

};

struct CAN_MVAL_21_BITS

{

bp_32 MsgVal:32; ///> 1:0 Message Valid Register 1

};

union CAN_MVAL_21_REG

{

bp_32 all;

struct CAN_MVAL_21_BITS bit;

};

struct CAN_IP_MUX21_BITS

{

bp_32 IntMux:32; ///> 1:0 Message Valid Register 1

};

union CAN_IP_MUX21_REG

{

bp_32 all;

struct CAN_IP_MUX21_BITS bit;

};

struct CAN_IF3UPD_BITS

{

bp_32 IF3UpdEn:32; ///> 1:0 Message Valid Register 1

};

union CAN_IF3UPD_REG

{

bp_32 all;

struct CAN_IF3UPD_BITS bit;

};

struct CAN_IFxCMD_BITS

{

bp_16 MSG_NUM:8; ///> 7:0 Message Number

bp_16 rsvd1:6; ///> 13:8 Reserved

bp_16 rsvd2:1; ///> 14 Reserved

bp_16 Busy:1; ///> 15 Busy Flag

bp_32 DATA_B:1; ///> 16 Access Data Bytes 4-7

bp_32 DATA_A:1; ///> 17 Access Data Bytes 0-3

bp_32 TXRQST:1; ///> 18 Access Transmission Request Bit

bp_32 ClrIntPnd:1; ///> 19 Clear Interrupt Pending Bit

bp_32 Control:1; ///> 20 Access Control Bits

bp_32 Arb:1; ///> 21 Access Arbitration Bits

bp_32 Mask:1; ///> 22 Access Mask Bits

bp_32 DIR:1; ///> 23 Write/Read Direction

bp_32 rsvd3:8; ///> 31:24 Reserved

};

union CAN_IFxCMD_REG

{

bp_32 all;

struct CAN_IFxCMD_BITS bit;

};

struct CAN_IFxMSK_BITS

{

bp_32 Msk:29; ///> 28:0 Identifier Mask

bp_32 rsvd1:1; ///> 29 Reserved

bp_32 MDir:1; ///> 30 Mask Message Direction

bp_32 MXtd:1; ///> 31 Mask Extended Identifier

};

union CAN_IFxMSK_REG

{

bp_32 all;

struct CAN_IFxMSK_BITS bit;

};

struct CAN_IFxARB_BITS

{

bp_32 ID:29; ///> 28:0 `

bp_32 Dir:1; ///> 29 Message Direction

bp_32 Xtd:1; ///> 30 Extended Identifier

bp_32 MsgVal:1; ///> 31 Message Valid

};

union CAN_IFxARB_REG

{

bp_32 all;

struct CAN_IFxARB_BITS bit;

};

struct CAN_IFxMCTL_BITS

{

bp_16 DLC:4; ///> 3:0 Data length code

bp_16 rsvd1:3; ///> 6:4 Reserved

bp_16 EoB:1; ///> 7 End of Block

bp_16 TxRqst:1; ///> 8 Transmit Request

bp_16 RmtEn:1; ///> 9 Remote Enable

bp_16 RxIE:1; ///> 10 Receive Interrupt Enable

bp_16 TxIE:1; ///> 11 Transmit Interrupt Enable

bp_16 UMask:1; ///> 12 Use Acceptance Mask

bp_16 IntPnd:1; ///> 13 Interrupt Pending

bp_16 MsgLst:1; ///> 14 Message Lost

bp_16 NewDat:1; ///> 15 New Data

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_IFxMCTL_REG

{

bp_32 all;

struct CAN_IFxMCTL_BITS bit;

};

struct CAN_IFxDATA_BITS

{

bp_16 Data_0:8; ///> 7:0 Data Byte 0

bp_16 Data_1:8; ///> 15:8 Data Byte 1

bp_32 Data_2:8; ///> 23:16 Data Byte 2

bp_32 Data_3:8; ///> 31:24 Data Byte 3

};

union CAN_IFxDATA_REG

{

bp_32 all;

struct CAN_IFxDATA_BITS bit;

};

struct CAN_IFxDATB_BITS

{

bp_16 Data_4:8; ///> 7:0 Data Byte 4

bp_16 Data_5:8; ///> 15:8 Data Byte 5

bp_32 Data_6:8; ///> 23:16 Data Byte 6

bp_32 Data_7:8; ///> 31:24 Data Byte 7

};

union CAN_IFxDATB_REG

{

bp_32 all;

struct CAN_IFxDATB_BITS bit;

};

struct CAN_IF3OBS_BITS

{

bp_16 Mask:1; ///> 0 Mask data read observation

bp_16 Arb:1; ///> 1 Arbitration data read observation

bp_16 Ctrl:1; ///> 2 Ctrl read observation

bp_16 Data_A:1; ///> 3 Data A read observation

bp_16 Data_B:1; ///> 4 Data B read observation

bp_16 rsvd1:3; ///> 7:5 Reserved

bp_16 IF3SM:1; ///> 8 IF3 Status of Mask data read access

bp_16 IF3SA:1; ///> 9 IF3 Status of Arbitration data read access

bp_16 IF3SC:1; ///> 10 IF3 Status of Control bits read access

bp_16 IF3SDA:1; ///> 11 IF3 Status of Data A read access

bp_16 IF3SDB:1; ///> 12 IF3 Status of Data B read access

bp_16 rsvd2:2; ///> 14:13 Reserved

bp_16 IF3Upd:1; ///> 15 IF3 Update Data

bp_32 rsvd3:16; ///> 31:16 Reserved

};

union CAN_IF3OBS_REG

{

bp_32 all;

struct CAN_IF3OBS_BITS bit;

};

struct CAN_IF3MSK_BITS

{

bp_32 Msk:29; ///> 28:0 Mask

bp_32 rsvd1:1; ///> 29 Reserved

bp_32 MDir:1; ///> 30 Mask Message Direction

bp_32 MXtd:1; ///> 31 Mask Extended Identifier

};

union CAN_IF3MSK_REG

{

bp_32 all;

struct CAN_IF3MSK_BITS bit;

};

struct CAN_IF3ARB_BITS

{

bp_32 ID:29; ///> 28:0 Message Identifier

bp_32 Dir:1; ///> 29 Message Direction

bp_32 Xtd:1; ///> 30 Extended Identifier

bp_32 MsgVal:1; ///> 31 Message Valid

};

union CAN_IF3ARB_REG

{

bp_32 all;

struct CAN_IF3ARB_BITS bit;

};

struct CAN_IF3MCTL_BITS

{

bp_16 DLC:4; ///> 3:0 Data length code

bp_16 rsvd1:3; ///> 6:4 Reserved

bp_16 EoB:1; ///> 7 End of Block

bp_16 TxRqst:1; ///> 8 Transmit Request

bp_16 RmtEn:1; ///> 9 Remote Enable

bp_16 RxIE:1; ///> 10 Receive Interrupt Enable

bp_16 TxIE:1; ///> 11 Transmit Interrupt Enable

bp_16 UMask:1; ///> 12 Use Acceptance Mask

bp_16 IntPnd:1; ///> 13 Interrupt Pending

bp_16 MsgLst:1; ///> 14 Message Lost

bp_16 NewDat:1; ///> 15 New Data

bp_32 rsvd2:16; ///> 31:16 Reserved

};

union CAN_IF3MCTL_REG

{

bp_32 all;

struct CAN_IF3MCTL_BITS bit;

};

struct CAN_IF3DATA_BITS

{

bp_16 Data_0:8; ///> 7:0 Data Byte 0

bp_16 Data_1:8; ///> 15:8 Data Byte 1

bp_32 Data_2:8; ///> 23:16 Data Byte 2

bp_32 Data_3:8; ///> 31:24 Data Byte 3

};

union CAN_IF3DATA_REG

{

bp_32 all;

struct CAN_IF3DATA_BITS bit;

};

struct CAN_IF3DATB_BITS

{

bp_16 Data_4:8; ///> 7:0 Data Byte 4

bp_16 Data_5:8; ///> 15:8 Data Byte 5

bp_32 Data_6:8; ///> 23:16 Data Byte 6

bp_32 Data_7:8; ///> 31:24 Data Byte 7

};

union CAN_IF3DATB_REG

{

bp_32 all;

struct CAN_IF3DATB_BITS bit;

};

struct CAN_REGS

{

union CAN_CTL_REG CAN_CTL; ///> CAN Control Register

union CAN_ES_REG CAN_ES; ///> Error and Status Register

union CAN_ERRC_REG CAN_ERRC; ///> Error Counter Register

union CAN_BTR_REG CAN_BTR; ///> Bit Timing Register

union CAN_INT_REG CAN_INT; ///> Interrupt Register

union CAN_TEST_REG CAN_TEST; ///> Test Register

uint32_t rsvd1[2]; ///> Reserved

union CAN_PERR_REG CAN_PERR; ///> CAN Parity Error Code Register

uint32_t rsvd2[16]; ///> Reserved

union CAN_RAM_INIT_REG CAN_RAM_INIT; ///> CAN RAM Initialization Register

uint32_t rsvd3[6]; ///> Reserved

union CAN_GLB_INT_EN_REG CAN_GLB_INT_EN; ///> CAN Global Interrupt Enable Register

union CAN_GLB_INT_FLG_REG CAN_GLB_INT_FLG; ///> CAN Global Interrupt Flag Register

union CAN_GLB_INT_CLR_REG CAN_GLB_INT_CLR; ///> CAN Global Interrupt Clear Register

uint32_t rsvd4[18]; ///> Reserved

union CAN_ABOTR_REG CAN_ABOTR; ///> Auto-Bus-On Time Register

union CAN_TXRQ_X_REG CAN_TXRQ_X; ///> CAN Transmission Request Register

union CAN_TXRQ_21_REG CAN_TXRQ_21; ///> CAN Transmission Request 2_1 Register

uint32_t rsvd5[6]; ///> Reserved

union CAN_NDAT_X_REG CAN_NDAT_X; ///> CAN New Data Register

union CAN_NDAT_21_REG CAN_NDAT_21; ///> CAN New Data 2_1 Register

uint32_t rsvd6[6]; ///> Reserved

union CAN_IPEN_X_REG CAN_IPEN_X; ///> CAN Interrupt Pending Register

union CAN_IPEN_21_REG CAN_IPEN_21; ///> CAN Interrupt Pending 2_1 Register

uint32_t rsvd7[6]; ///> Reserved

union CAN_MVAL_X_REG CAN_MVAL_X; ///> CAN Message Valid Register

union CAN_MVAL_21_REG CAN_MVAL_21; ///> CAN Message Valid 2_1 Register

uint32_t rsvd8[8]; ///> Reserved

union CAN_IP_MUX21_REG CAN_IP_MUX21; ///> CAN Interrupt Multiplexer 2_1 Register

uint32_t rsvd9[18]; ///> Reserved

union CAN_IFxCMD_REG CAN_IF1CMD; ///> IF1 Command Register

union CAN_IFxMSK_REG CAN_IF1MSK; ///> IF1 Mask Register

union CAN_IFxARB_REG CAN_IF1ARB; ///> IF1 Arbitration Register

union CAN_IFxMCTL_REG CAN_IF1MCTL; ///> IF1 Message Control Register

union CAN_IFxDATA_REG CAN_IF1DATA; ///> IF1 Data A Register

union CAN_IFxDATB_REG CAN_IF1DATB; ///> IF1 Data B Register

uint32_t rsvd10[4]; ///> Reserved

union CAN_IFxCMD_REG CAN_IF2CMD; ///> IF2 Command Register

union CAN_IFxMSK_REG CAN_IF2MSK; ///> IF2 Mask Register

union CAN_IFxARB_REG CAN_IF2ARB; ///> IF2 Arbitration Register

union CAN_IFxMCTL_REG CAN_IF2MCTL; ///> IF2 Message Control Register

union CAN_IFxDATA_REG CAN_IF2DATA; ///> IF2 Data A Register

union CAN_IFxDATB_REG CAN_IF2DATB; ///> IF2 Data B Register

uint32_t rsvd11[4]; ///> Reserved

union CAN_IF3OBS_REG CAN_IF3OBS; ///> IF3 Observation Register

union CAN_IF3MSK_REG CAN_IF3MSK; ///> IF3 Mask Register

union CAN_IF3ARB_REG CAN_IF3ARB; ///> IF3 Arbitration Register

union CAN_IF3MCTL_REG CAN_IF3MCTL; ///> IF3 Message Control Register

union CAN_IF3DATA_REG CAN_IF3DATA; ///> IF3 Data A Register

union CAN_IF3DATB_REG CAN_IF3DATB; ///> IF3 Data B Register

uint32_t rsvd12[4]; ///> Reserved

union CAN_IF3UPD_REG CAN_IF3UPD; ///> IF3 Update Enable Register

};

}

}

}

}

}

#endif /* INCLUDE_F2837XD_CAN_IMPLEMENTATION_CAN_REGS_HPP_ */