Part Number: TDA2SX

Other Parts Discussed in Thread: SYSCONFIG

Tool/software: Code Composer Studio

hi,

I am using the emulator to debug PROCESSOR_SDK_VISION_03_08_00_00.

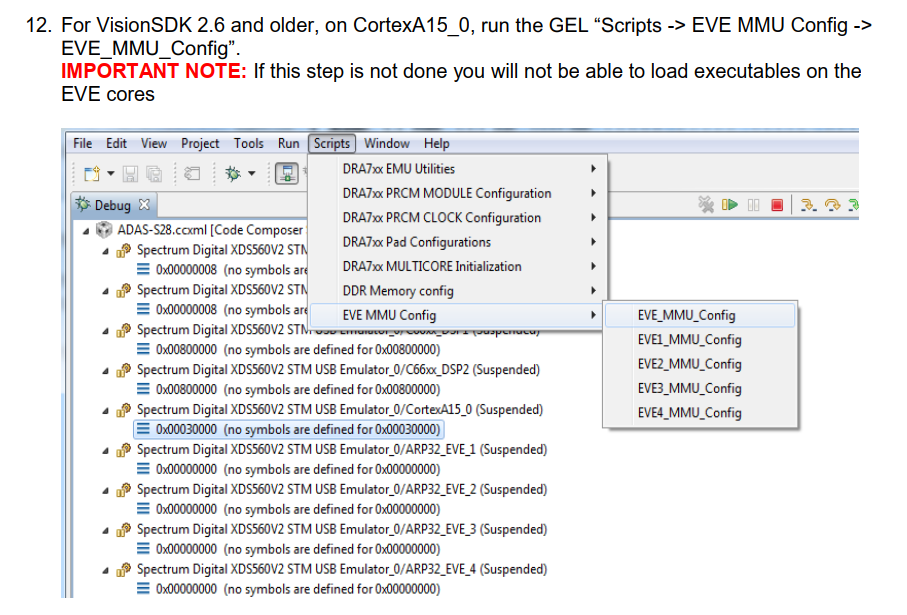

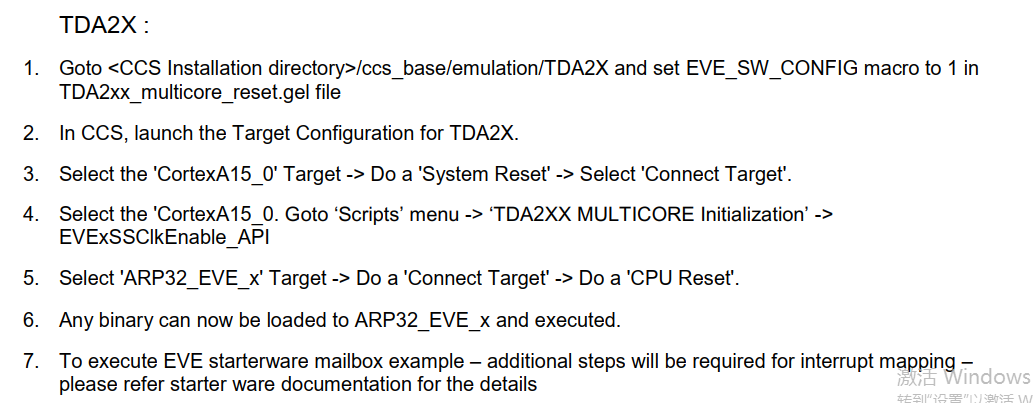

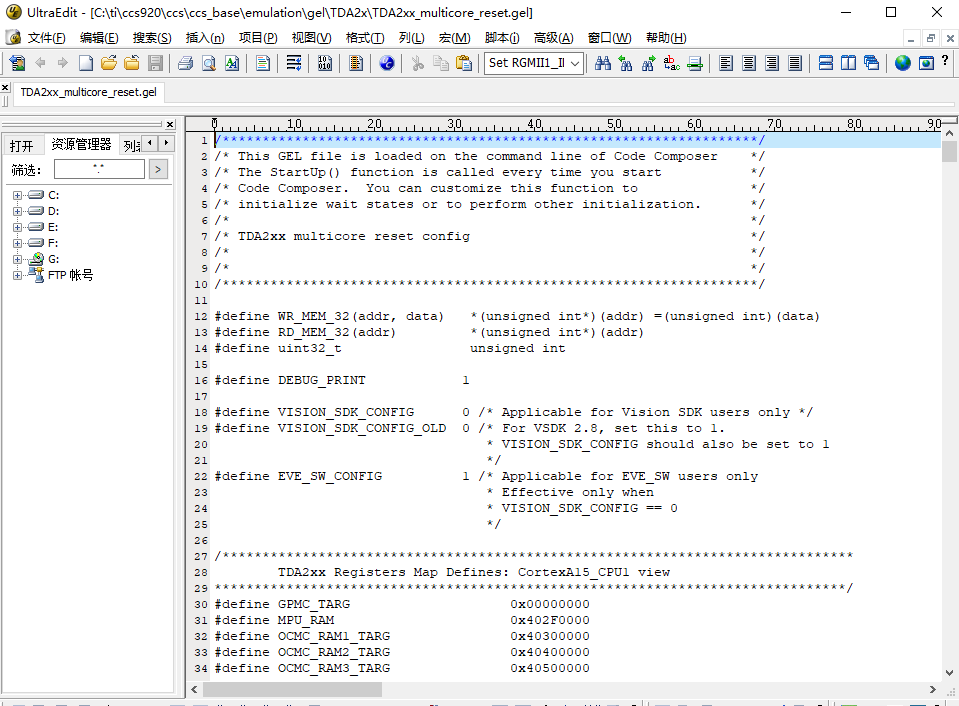

The description in the guidance document is this:

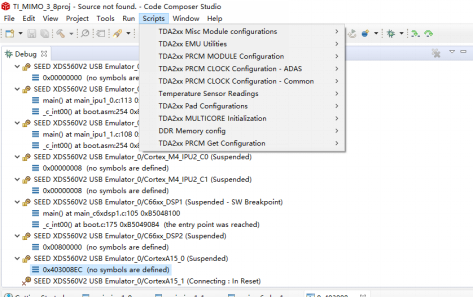

But I do not see EVE MMU config option in the Scripts menu:

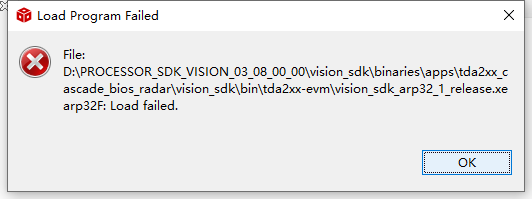

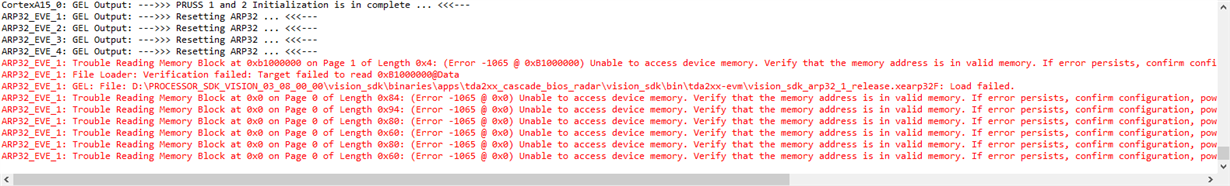

there is an Error when loading the EVE executable code:

Please help me solve this problem, thank you.