Tool/software: Code Composer Studio

Hi,

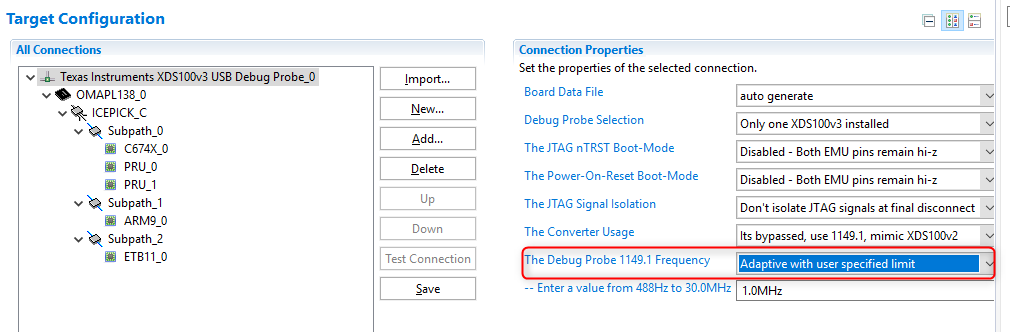

I'm trying to connect to the ARM9 inside the OMAP-L138 on the OMAP-L138LCDK dev board through an XDS100v3.

When the gel file from TI is launched prior to debug the below output is generated.

ARM9_0: Output: Target Connected.

ARM9_0: Output: ---------------------------------------------

ARM9_0: Output: Memory Map Cleared.

ARM9_0: Output: ---------------------------------------------

ARM9_0: Output: Memory Map Setup Complete.

ARM9_0: Output: ---------------------------------------------

ARM9_0: Output: PSC Enable Complete.

ARM9_0: Output: ---------------------------------------------

ARM9_0: GEL: Error while executing OnTargetConnect(): Target failed to write 0x01C11138

at (*((unsigned int *) (0x01C11000+0x138))|=0x1) [OMAP-L138_LCDK.gel:16]

at device_PLL0(0, 24, 1, 0, 1, 11, 5) [OMAP-L138_LCDK.gel:403]

at Set_Core_300MHz() [OMAP-L138_LCDK.gel:468]

at Core_300MHz_mDDR_150MHz() [OMAP-L138_LCDK.gel:245]

at OnTargetConnect()

I found the below thread which talks about this same issue, but I don't think the probe I'm using falls into the same category.

https://e2e.ti.com/support/tools/ccs/f/81/p/786780/2912086#2912086

Should it only be the J-TAG settings then that's the issue?

Thanks,

Ben