Other Parts Discussed in Thread: OPA2376, OPA2189, OPA2192, CSD22206W, CSD23285F5

Hi team,

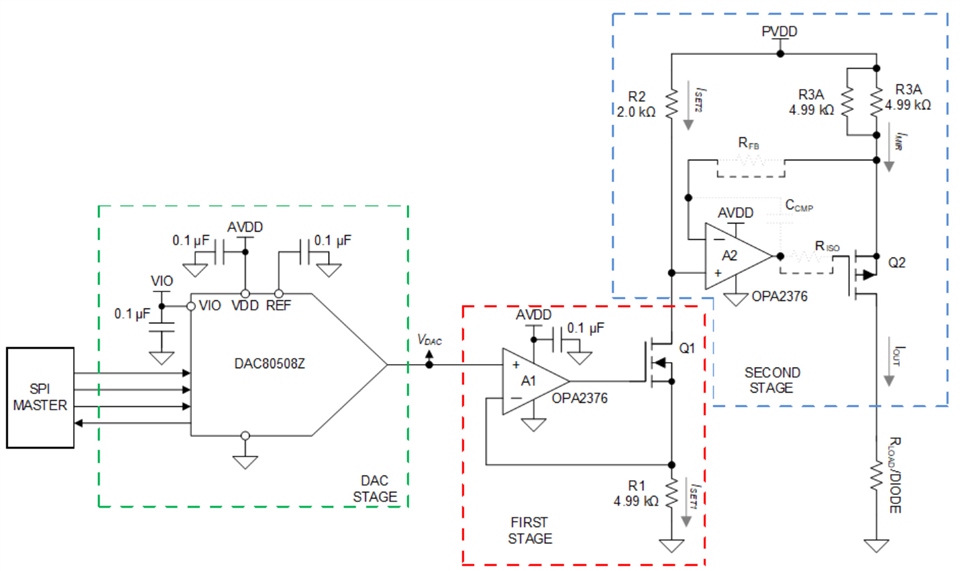

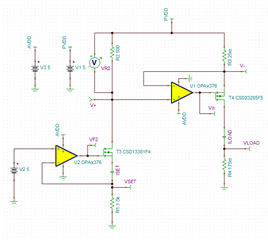

The figure is the voltage controlled current mirror circuit diagram of TIDA-01525.

I want to configure Rload be about 3.5V LED within 1~15A (wannabe 1~20A) contant current.

PVDD, AVDD, max of VDAC is 5V.

1. Assuming that the power of Q2 and R3 is sufficient, is there a limit to the maximum IOUT and Watt that can be applied?

(or limited by the amplification ratio of Iset2 and Imir)

2. If possible, what are the main considerations in this configuration?

3. Can you suggest a design for this?

Thank you.

Hoo