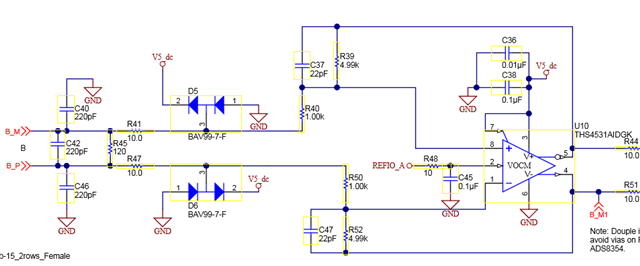

Other Parts Discussed in Thread: THS4531, , ADS8354, THS4531A

Hi Team,

Good day. I am posting this inquiry on behalf of the customer.

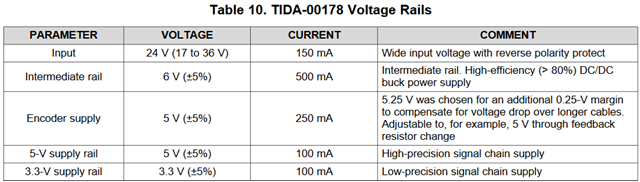

I would like to take over the reference design TIDA-00178 for a project. In the example project, a gain factor of 5 is set for the THS4531.

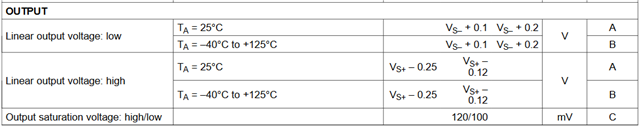

As a power supply, the chip has 5 V. If I amplify 1Vpp by 5, then I have between 0 and 5V. The output voltages do not go up to 5 V, but rather 4.9 V.

If my 5V power supply fluctuates by 5%, it gets even less.

So with a gain of 5, I will have problems in the 0V and 5V limits.

The signal is cut off above and below.

What am I missing here? I'd love it if you could help me.

Thank you for extending your support. Your help is much appreciated.

Kind regards,

Marvin