Other Parts Discussed in Thread: CSD25310Q2, CSD17483F4, CSD13380F3, TINA-TI

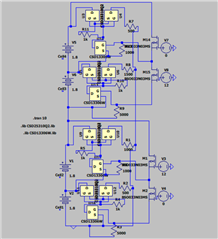

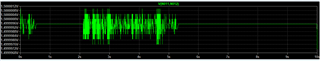

In the attached picture, CSD13306W is the NMOS model and CSD25310Q2 is the PMOS model. PMOS switches are in SSR configuration. The circuit is such that nmos switch is used to trigger PMOS switches in ssr configuration .In row of cell 3, transient spikes are coming in the voltage graph of VGS of NMOS ,though these transients are in uV. The graph is also attached .Additionally, no such transient can be seen if the resistance next to the PMOS is adjusted to raise the drain current through the PMOS to 5 A. In other rows, where VGS is not 1.5, no transient can be observed. What is the reason behind these transients in Vgs graph of NMOS when Vgs is 1.5V?

Vgs Graph through NMOS of Cell3