Tool/software:

Hello,

We’re encountering issues with our design when running the "Steady State Operation, Operational Voltage Range" test, as specified in Section 5.3.1.1 of the MIL-1275 standard. Here are the details of our setup and the problem we're facing:

Design Details:

- We are using a modified reference design, where the only change is a higher current MOSFET to meet our 15A requirement.

- Instead of the original MOSFETs (IXTT88N30P and SQJQ466E-T1_GE3), we are using IXFK220N17T2

Issue Observed:

During the test, we noticed the following components were damaged:

- MOSFET connected to the H-Gate (IXFK220N17T2) in the first clamping circuit was shorted across all pins.

- 47µF electrolytic capacitor on the output side of the first stage was bulged.

- IC LM74800QDRRRQ1 in the first stage clamping circuit was damaged.

- IC LM5060Q1MMX/NOPB in the second stage clamping circuit was also damaged.

Test Results:

- The test passed with a 200mA load on a different unit.

- However, the test fails with higher currents (~3A and 9A).

We would appreciate any insights or suggestions to diagnose and resolve these issues. Thank you!

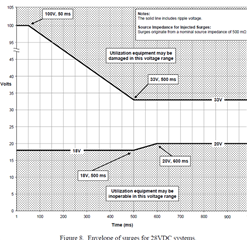

The voltage profile applied at Vin is given below . test start with 28V and switched to 100V(slew 100mS) and followed the below profile