Tool/software:

Hi, I have some questions regarding the simulation file.

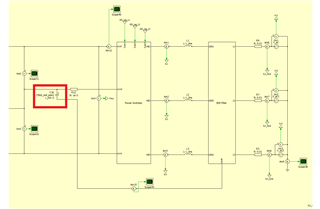

In the PLECs simulation, there is a capacitor Cfdck_mid_point connecting the DC bus midpoint to the filter caps in the LCL. This cap is not present in the design guide. Is it a parasitic cap? Is it needed in the final design? How can I determine an appropriate value for this cap?

Also, the grid side inductor is a common core inductor. Is it recommended to use a common core inductor or just 3 seperate inductors? How to determine the value of Lcommon?