Tool/software:

Hello,

when checking the design a couple of question came up on my end.

In general my questions are linked to what is really needed to archive SIL 3. Reason for asking this is that we have a space and loss restricted application.

1. Are digital isolators are needed for the STO_1 and STO_2 signals?

2. When checking the standard, I have not recognized the need for implementing the STO_FB. Is my assumption correct that this was implemented to give users some feedback when they get familiar with the Eval board?

3. In our application we use non-isolated gate driver (48V application (MOSFETS are used in the bridge). Do you see any issues here with still reaching SIL 3

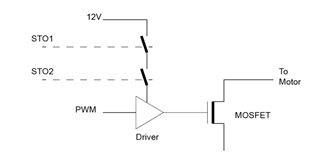

Here just some side information... As mentioned we are currently are using a non-isolated gate driver. In our current concept we still have two STO lines (STO_1 and STO_2). These signals are connected to a switch. The two switches (one for STO_1 and the second one for STO_2) are in series and will ensure that the supply of the gate driver will be disconnected when the STO gets low. (A simple version of this you can see in the following figure [ I am aware that diagnostic, filter, ... are not shown here])

Would be great if someone is able to answer them =)

Thank you