Tool/software:

Dear Team,

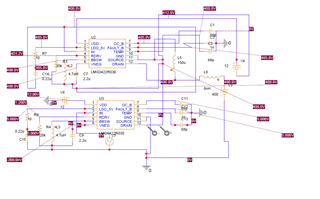

I am currently working with the LMG3422R030 GaN FET using the synchronous buck evaluation board and am facing a few issues that I need assistance with. Below are the details of my queries:

- Issue with LDO Pin Connection:

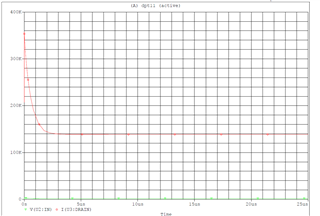

- When I connect the LDO pin through a 10-ohm resistor in series with a 0.22 µF capacitor, I am unable to obtain the expected simulation results. Could you please clarify if there are additional considerations or configurations needed for proper operation in this setup?

- Alternatively, when I connect the LDO pin to the 5V LDO output as per the datasheet, I should observe a slew rate of 100 V/ns. However, the circuit is not functioning as expected. Could you provide guidance on troubleshooting this issue?

- Understanding Q1 Low-Side Switch:

- I am looking for a detailed explanation of how the Q1 switch, located on the low side, helps to reduce the slew rate of the low-side switch during turn-on. I’m unable to fully grasp the underlying mechanism, so any clarification would be appreciated.

- Isolator for High-Side Switches in H-Bridge:

- Could you advise if the same isolator can be used for both high-side switches in an H-bridge topology? If yes, are there any specific design considerations or limitations I should be aware of?

Your assistance in resolving these issues and providing the necessary clarifications will be greatly appreciated. Please let me know if you require additional details about the circuit or the simulation setup.

Best Regards

B Raja Sekhar