Tool/software:

Hello,

I am working with TPA3136D2 and would like to clarify a question regarding its duty cycle behavior during output clipping.

According to the datasheet:

9.1 Overview

"These capacitors ensure sufficient energy storage, even during clipped low frequency audio signals, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of its ON cycle."

9.3.3 PLIMIT

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to a fixed maximum value. The limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. The "virtual" rail is approximately four times the voltage at the PLIMIT pin. The output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

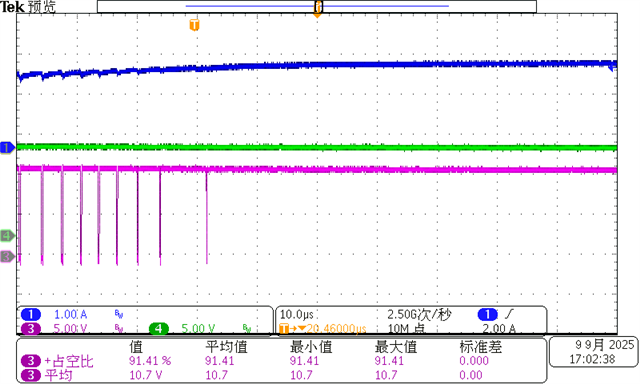

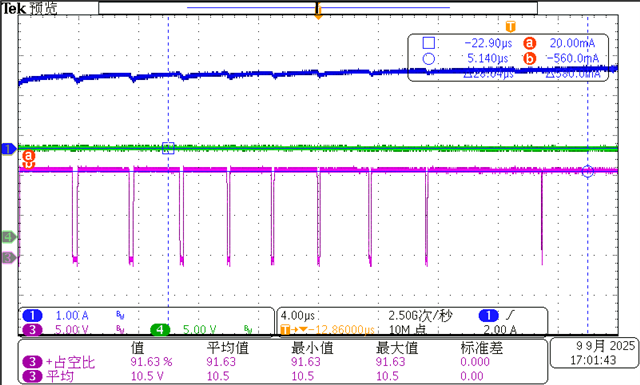

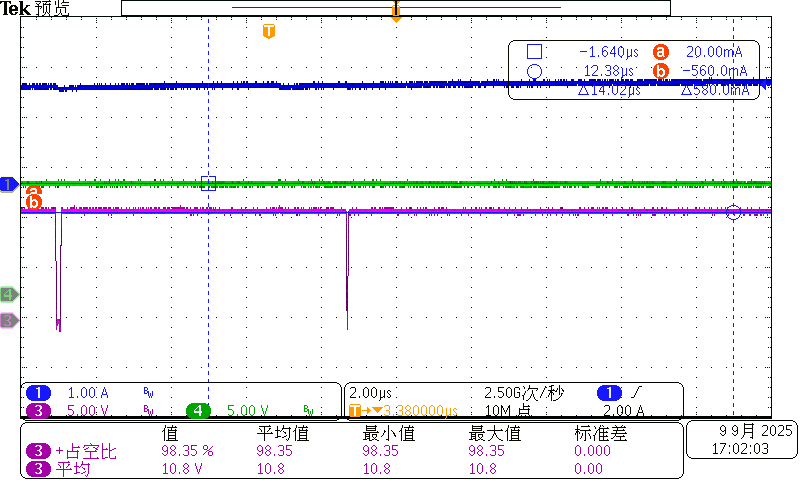

From my measurements, it appears that during clipping, the OUTNL/OUTNR duty cycle can reach 100%. I would like to confirm whether this IC is indeed capable of achieving a full 100% duty cycle.

My circuit configuration is as follows:

-

AVCC = 12 V

-

RL = 4 Ω

-

PLIMIT = 1/2*GVDD

-

BTL mode = Mono PBTL mode

- Speaker output power ≈ 3 W

Attached are three waveform screenshots showing the duty cycle approaching 100% during clipping. Could anyone confirm if my observation is correct or if there is something I might be overlooking in this configuration?

Thank you in advance for your insights!