Tool/software:

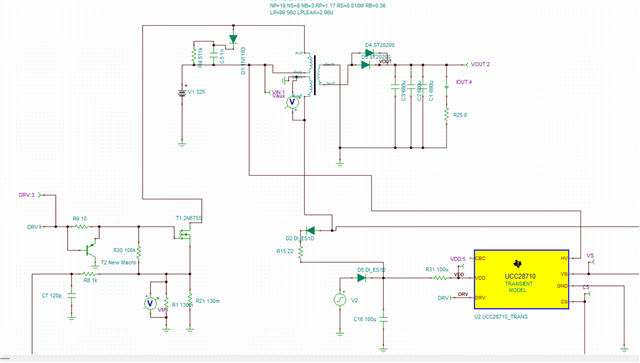

I have designed an AC/DC charger with specifications of 54V / 200W for a battery bank. An open-loop simulation was carried out without implementing Primary-Side Regulation (PSR), and the expected output was obtained. The corresponding simulation file is attached for reference.

Battery charger - autosave 25-09-10 18_56 (1).TSC

But when I try to run the closed-loop simulation, the DRV signal is not generated. The corresponding simulation file is attached for reference.

Battery charger with feedback - autosave 25-09-11 10_42.TSC

Please suggest the possible reason and solution for this issue.

Regards,

Kalyani