Other Parts Discussed in Thread: TINA-TI

Tool/software:

Hi team,

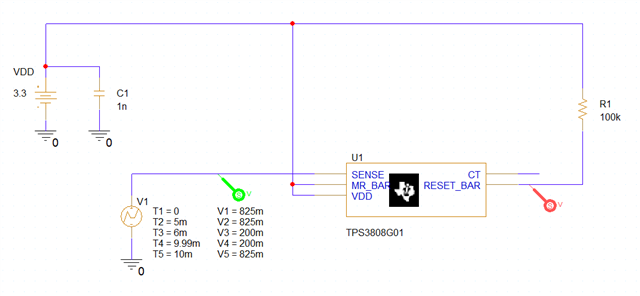

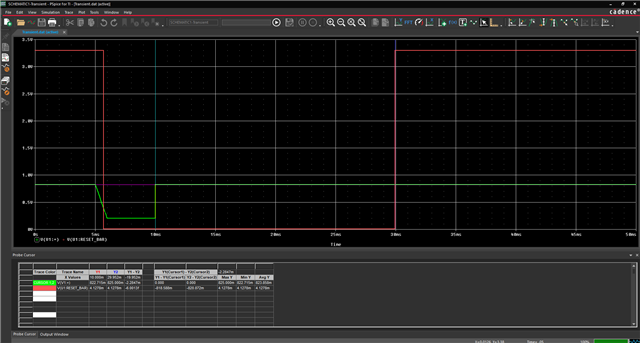

We used TPS3808G01-Q1 for monitoring one of the rails in our board. When we are simulating the circuit in ltspice with CT pin in the IC, we observed below behaviour in RESET assertion. Pease provide a rationale for this:

When we added some glitch pulse on monitored rail of sufficient overdrive and transient duration, the RESET got asserted to low as and when the SENSE voltage is less than 0.405V. But the RESET is not De-asserting to high after a delay of 20msec when monitoted rail reaches the Release threshold on SENSE pin with CT left unconnected.

We tried connecting a 3.3nF capacitor at CT pin which will produce a delay of around 19.5msec, then the RESET is de asserting to high when monitored rail reaches its release threshold after a set delay.

can you please help on this