Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

Hi,

I simualted the rise/fall time of FET(CSD15380F3). But the simulated results and datasheet specs are different.

In the datasheet, the test conditions are Vds=10V, Vgs=4.5V, Rg=0Ohm, Ids=0.1A. And the rise time is 1ns and fall time is 7ns.

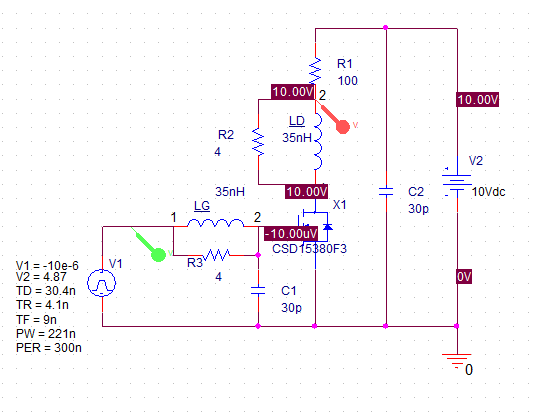

Therefore, in the simulation, I connected 0Ohm and 100Ohm to the gate and drain of FET, respectively. Vds is 10V and Vgs is 4.5V pulse.(I set the rise/fall time of Vgs is 1ps.)

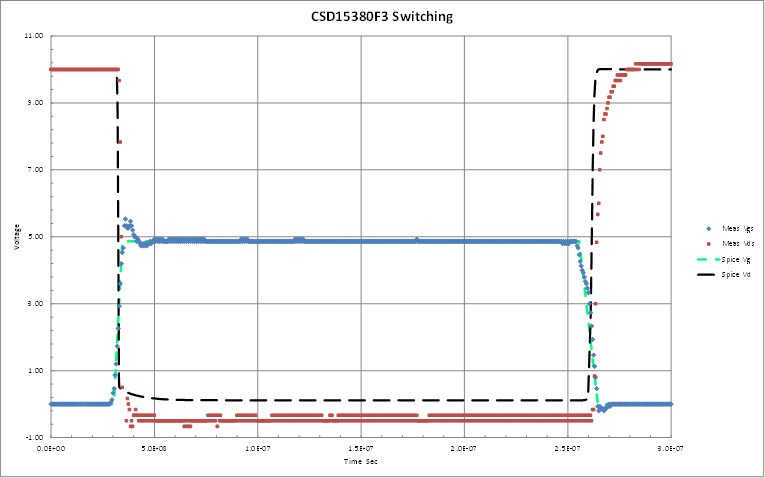

But in my simulation results, rise time is 1.6ns and fall time is 1.6ns.

What is wrong in my simulation setting?

How to simulate the rise and fall time of FET?