Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

I am trying to use OP189 amplifiers to monitor and control currents. I attached the simulation file.

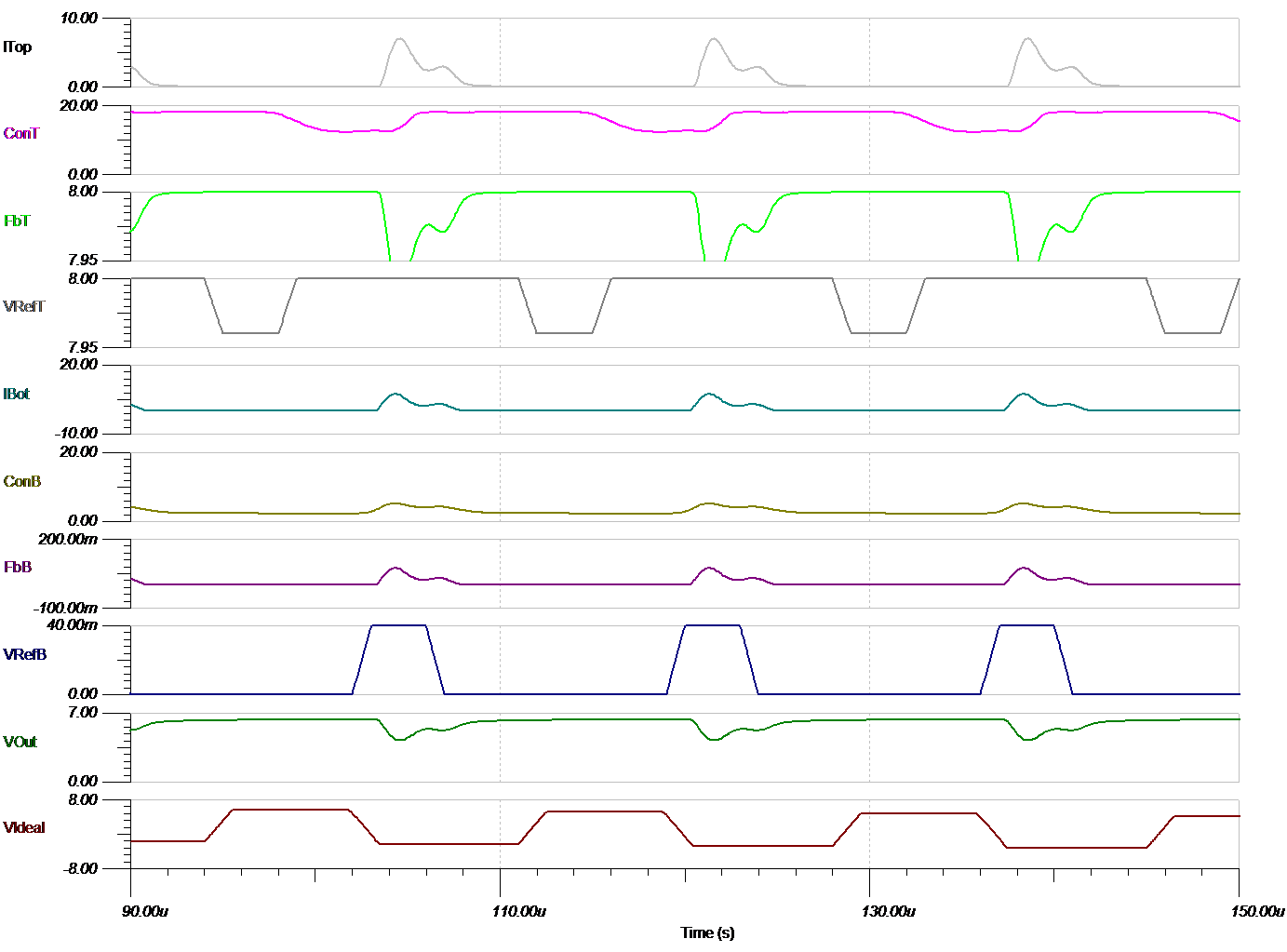

The circuit is unstable at a low frequency. If you run the simulation, you can see it performs as expected for a few cycles about 444us after the start. Then it goes astray and returns later for another few cycles.

There is a second ideal test circuit in the design to demonstrate the ideal output waveform. The test circuit using an ideal supply and ideal capacitor also seems to wonder so something I do not understand is affecting the circuit simulation.

Looking at the inputs and output of the OPA189 it seems to quit trying to control properly. I suspect something is just wrong with my simulation setup.

I think the circuit can work because I see it perform as expected, briefly. I have not found any way to make it more stable.

I am open to any ideas to modify the simulation, tweak this circuit, swap parts, or redesign completely to meet the goals described in the schematic.