Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

Hello,

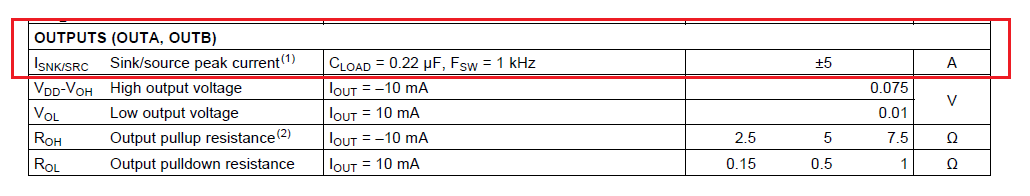

I am using the unencrypted pspice transient model for UCC27524 in LTspice. As an experiment, I connected the driver output directly to a 8100pF capacitor with no external gate resistor in the simulation. Purpose is to verify the dynamic pull high an pull low resistance inside the gate driver. The simulated gate pulse current is less than 4.2A for both pull high and pull low, while the gate driver is powered by 7.5V voltage source. This indicates the internal resistance is around 1.7 ohm which is larger than datasheet value. The power supply is then increased to 15V. This time the gate current peak is clamped flat to 5.30A(source) and 5.65A(sink). Increasing the power supply voltage doesn't change the clamped peak current amplitude.

Can you clarify if the unencrypted pspice model is accurate regarding the gate current pulse? Is the model reliable to evaluate the dynamic internal resistance of the driver during switching transience? Is the TINA model or encrypted pspice model more accurate? Does the physical device also have output current clamp?

Thank you.

Zhenyu