Other Parts Discussed in Thread: OPA197, OPA170, OPA171

Tool/software: WEBENCH® Design Tools

Hello Colleagues,

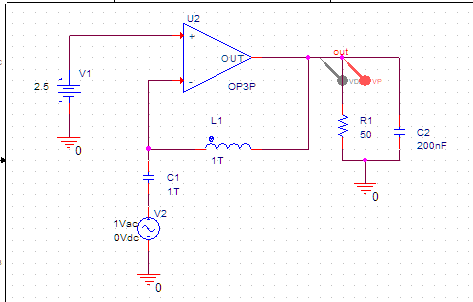

I am working on a simulation for a customer and use Allegro PSpice 17.2 (our corporate license). Unfortunately, I am not able to get any results. Most of the time the simulation fails due to "ERROR -- Convergence problem in transient bias point calculation". This is unfortunately true also for our test circuit that is a part of the ALM2402F-Q1 PSPICE Model package at the product page. It is not the first time this is happening to me. I often encounter convergence issues with opamp pSpice models from TI (e.g. opa 170,171,197 etc.).

A colleague of mine tried the same and has the same issue. This indicates that there is something wrong with the default configuration of the pSpice engine.

Does anyone from the Webench team have an idea what could be the root cause?

Below is the failed output file for the provided test circuit.

Best regards,

Jiri Panacek

Systems Engineer at SEM-Powertrain

**** 02/17/20 14:34:07 ****** PSpice 17.2.0 (March 2016) ****** ID# 0 ********

** Profile: "SCHEMATIC1-ALM2402F test circuit" [ c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\schematic1\alm2402f te

**** CIRCUIT DESCRIPTION

******************************************************************************

** Creating circuit file "ALM2402F test circuit.cir"

** WARNING: THIS AUTOMATICALLY GENERATED FILE MAY BE OVERWRITTEN BY SUBSEQUENT SIMULATIONS

*Libraries:

* Profile Libraries :

* Local Libraries :

.LIB "../../../alm2402f test circuit-pspicefiles/alm2402f.lib"

* From [PSPICE NETLIST] section of C:\Users\a0406914\AppData\Roaming\SPB_Data\cdssetup\OrCAD_PSpice\17.2.0\PSpice.ini file:

.lib "nom.lib"

*Analysis directives:

.TRAN 0 2m 0 2u

.OPTIONS ADVCONV

.OPTIONS WIDTH= 132

.PROBE64 V(alias(*)) I(alias(*)) W(alias(*)) D(alias(*)) NOISE(alias(*))

.INC "..\SCHEMATIC1.net"

**** INCLUDING SCHEMATIC1.net ****

* source ALM2402F TEST CIRCUIT

V_V1 N15016 N149961 AC 1

+SIN 0 100m 1k 0 0 0

R_RL 0 OUT R_RL 2k TC=0,0

.model R_RL RES R=1 DEV=10% TC1=0 TC2=0

C_CL 0 OUT C_CL 15p TC=0,0

.model C_CL CAP C=1 DEV=10% TC1=0 TC2=0 VC1=0 VC2=0

V_VS +12V 0 12

V_V2 N149961 0 6

X_U1 N15016 OUT +12V +12V 0 OUT ALM2402F

**** RESUMING "ALM2402F test circuit.cir" ****

.END

WARNING(ORPSIM-15223): Library file "c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\alm2402f.lib" has changed since index file alm2402f.ind was created.

WARNING(ORPSIM-15227): The timestamp changed from Fri Aug 23 23:49:40 2019 to Fri Aug 23 13:49:42 2019.

INFO(ORPSIM-15422): Making new index file alm2402f.ind for library file alm2402f.lib.

Index has 17 entries from 1 file(s).

**** 02/17/20 14:34:07 ****** PSpice 17.2.0 (March 2016) ****** ID# 0 ********

** Profile: "SCHEMATIC1-ALM2402F test circuit" [ c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\schematic1\alm2402f te

**** Diode MODEL PARAMETERS

******************************************************************************

X_U1.X_IN_U12.DVN X_U1.X_IN_U7.DVN X_U1.X_IN_U8.DVN

IS 100.000000E-18 100.000000E-18 100.000000E-18

KF 10.000000E-12 316.227800E-12 10.000000E-12

**** 02/17/20 14:34:07 ****** PSpice 17.2.0 (March 2016) ****** ID# 0 ********

** Profile: "SCHEMATIC1-ALM2402F test circuit" [ c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\schematic1\alm2402f te

**** Resistor MODEL PARAMETERS

******************************************************************************

R_RL R_NOISELESS

T_Measured 27

T_Current -273.15

R 1 1

**** 02/17/20 14:34:07 ****** PSpice 17.2.0 (March 2016) ****** ID# 0 ********

** Profile: "SCHEMATIC1-ALM2402F test circuit" [ c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\schematic1\alm2402f te

**** Capacitor MODEL PARAMETERS

******************************************************************************

C_CL

C 1

**** 02/17/20 14:34:07 ****** PSpice 17.2.0 (March 2016) ****** ID# 0 ********

** Profile: "SCHEMATIC1-ALM2402F test circuit" [ c:\temp\alm2402f - pspice\alm2402f test circuit-pspicefiles\schematic1\alm2402f te

**** Voltage Controlled Switch MODEL PARAMETERS

******************************************************************************

X_U1.X_IN_U10.ESD_SW X_U1.X_U7.ESD_SW X_U1.X_ZO_U3.OL_SW

RON 50 50 1.000000E-03

ROFF 1.000000E+12 1.000000E+12 1.000000E+09

VON .5 .5 .9

VOFF .45 .45 .1

Starting pseudo-transient algorithm.

**** Param: RUNFOR = 0

ERROR -- Convergence problem in transient bias point calculation

Last node voltages tried were:

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( OUT) 6.0010 ( +12V) 12.0000 (N15016) 6.0000 (N149961) 6.0000 (X_U1.MID) 81.40E-09

(X_U1.CLAMP) 15.2880 (X_U1.VCC_B) 12.0000 (X_U1.VEE_B) 120.1E-09

(X_U1.VIMON) 3.0005 (X_U1.VSO_B) 12.0000 (X_U1.VOUT_S) 6.0010

(X_U1.VSENSE) 15.2880 (X_U1.N834543) 15.2880 (X_U1.N834559) 15.2880

(X_U1.N834565) 81.40E-09 (X_U1.N834719) 6.0010 (X_U1.N834755) 6.0011

(X_U1.N834759) 6.0000 (X_U1.N835353) 6.0010 (X_U1.N835455) 6.0010

(X_U1.N838247) 3.0005 (X_U1.N848133) 15.2880 (X_U1.GR_CL_OLN) 81.40E-09

(X_U1.GR_CL_OLP) 81.40E-09 (X_U1.X_IN_U7.3) 0.0000 (X_U1.X_IN_U7.4) 0.0000

(X_U1.X_IN_U7.5) 0.0000 (X_U1.X_IN_U7.6) 0.0000 (X_U1.X_IN_U7.7) .8338

(X_U1.X_IN_U7.8) .8338 (X_U1.X_IN_U8.3) 0.0000 (X_U1.X_IN_U8.4) 0.0000

(X_U1.X_IN_U8.5) 0.0000 (X_U1.X_IN_U8.6) 0.0000 (X_U1.X_IN_U8.7) .8338

(X_U1.X_IN_U8.8) .8338 (X_U1.IN_N808797) 6.0000 (X_U1.IQ_N785395) 12.0000

(X_U1.IQ_N785401) 81.40E-09 (X_U1.IQ_N785443) 120.1E-09 (X_U1.ISC_N51496) 81.40E-09

(X_U1.ISC_N51522) 81.40E-09 (X_U1.ISC_N51598) 81.40E-09 (X_U1.ISC_N51604) 81.40E-09

(X_U1.ISC_N51816) -550.0000 (X_U1.ISC_N51850) 700.0000 (X_U1.X_IN_U12.3) 0.0000

(X_U1.X_IN_U12.4) 0.0000 (X_U1.X_IN_U12.5) 0.0000 (X_U1.X_IN_U12.6) 0.0000

(X_U1.X_IN_U12.7) .8338 (X_U1.X_IN_U12.8) .8338 (X_U1.ZO_N918931) 1116.2000

(X_U1.ZO_N934374) 1116.2000 (X_U1.ZO_N942239) 917.3900 (X_U1.ZO_N942250) 19.5380

(X_U1.ZO_N947429) 1116.1000 (X_U1.ZO_N948588) 1116.4000 (X_U1.ZO_N948594) 1080.4000

(X_U1.ZO_N949563) 39.86E+03 (X_U1.ZO_N949752) 1116.1000 (X_U1.AOL_N625317) .0127

(X_U1.AOL_N948979) 15.2880 (X_U1.CLAW_N46077) 81.40E-09 (X_U1.CLAW_N46115) 81.40E-09

(X_U1.CLAW_N46221) 81.40E-09 (X_U1.CLAW_N46227) 81.40E-09 (X_U1.CLAW_N46501) 11.0030

(X_U1.CLAW_N46723) .0048 (X_U1.VOS_N811084) 6.0004 (X_U1.VOS_N811308) 6.0004

(X_U1.VOS_N811314) 81.40E-09 (X_U1.VOS_N812314) 674.5E-06 (X_U1.VOS_N812464) 6.0004

(X_U1.VOS_N812540) 6.0011 (X_U1.VOS_N824535) 6.0011 (X_U1.VOS_N827849) 60.06E-06

(X_U1.VOS_N829918) .2000 (X_U1.VOS_N831813) 7.0000 (X_U1.ZO_N9473211) 1116.1000

(X_U1.AOL_N9488531) 15.2880 (X_U1.CLAW_VCC_CLP) 11.0030 (X_U1.CLAW_VEE_CLP) .0048

(X_U1.GR_CL_N785752) 81.40E-09 (X_U1.GR_CL_N785794) 81.40E-09 (X_U1.GR_CL_N785870) 81.40E-09

(X_U1.GR_CL_N785876) 81.40E-09 (X_U1.GR_CL_N785976)-2500.0000 (X_U1.GR_CL_N786030) 2500.0000

(X_U1.GR_CL_N847200) 81.40E-09 (X_U1.GR_CL_N847308) 81.40E-09 (X_U1.GR_CL_N847364) -8.7118

(X_U1.GR_CL_N847418) 39.2880 (X_U1.GR_CL_N867266) 81.40E-09 (X_U1.VOS_CMRR_N949520) 60.06E-06

(X_U1.VOS_CMRR_N950135) .4614 (X_U1.VOS_CMRR_N950219) 60.06E-06 (X_U1.VOS_PSRR_N825009) 81.41E-09

(X_U1.VOS_PSRR_N949819) 10.1160 (X_U1.VOS_PSRR_N950583) 118.2E-09 (X_U1.VOS_PSRR_N951173) 81.41E-09

(X_U1.VOS_CMRR_N9494561) 60.06E-06

**** Interrupt ****