Tool/software: WEBENCH® Design Tools

Hello:

Use the official website pspice model-SLIM249B.ZIP (110 KB) - PSpice Model

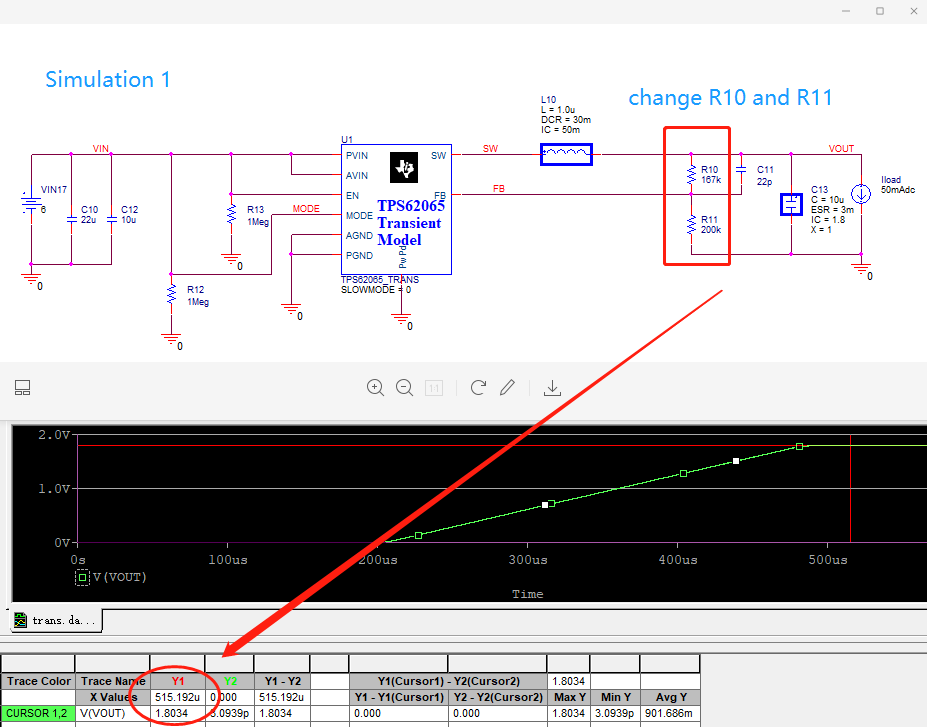

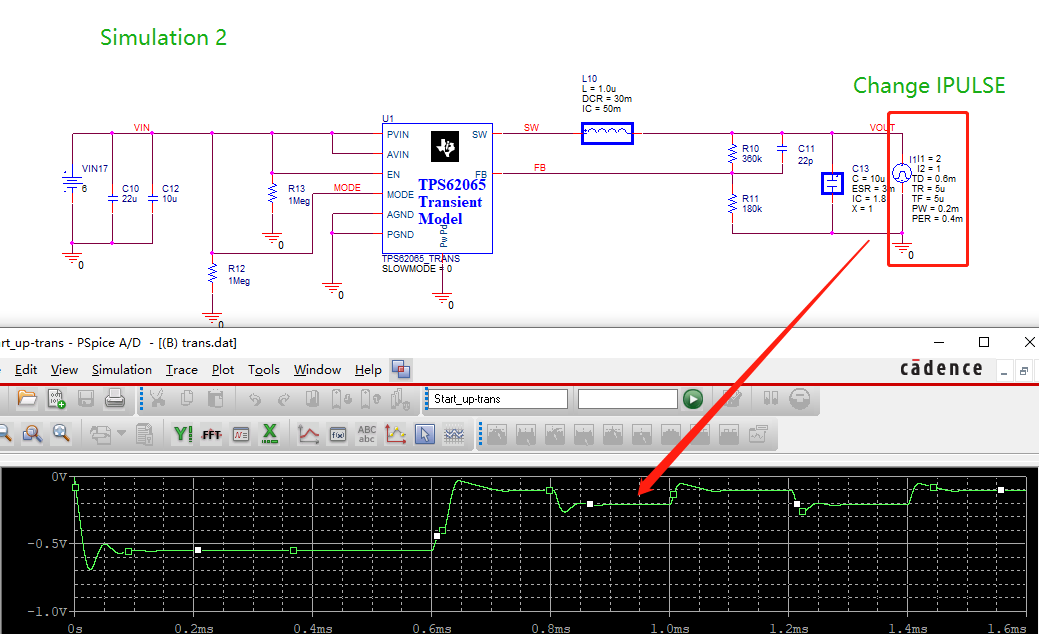

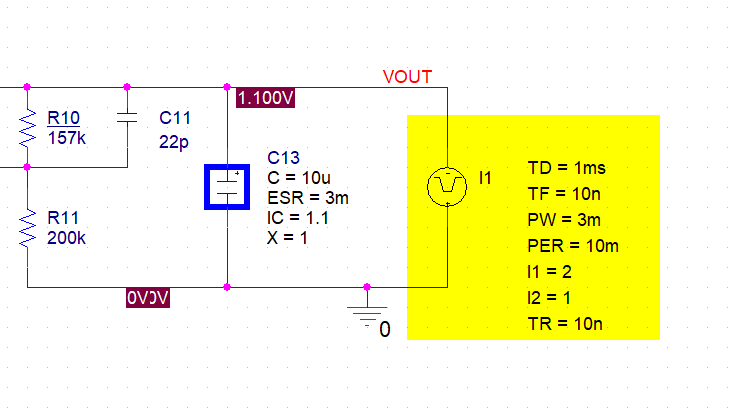

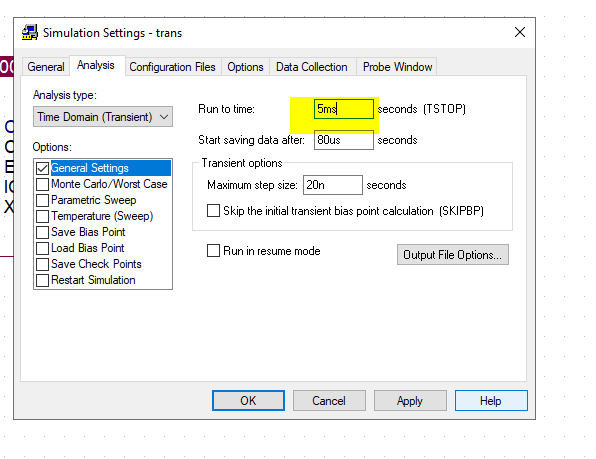

Simulation conditions:

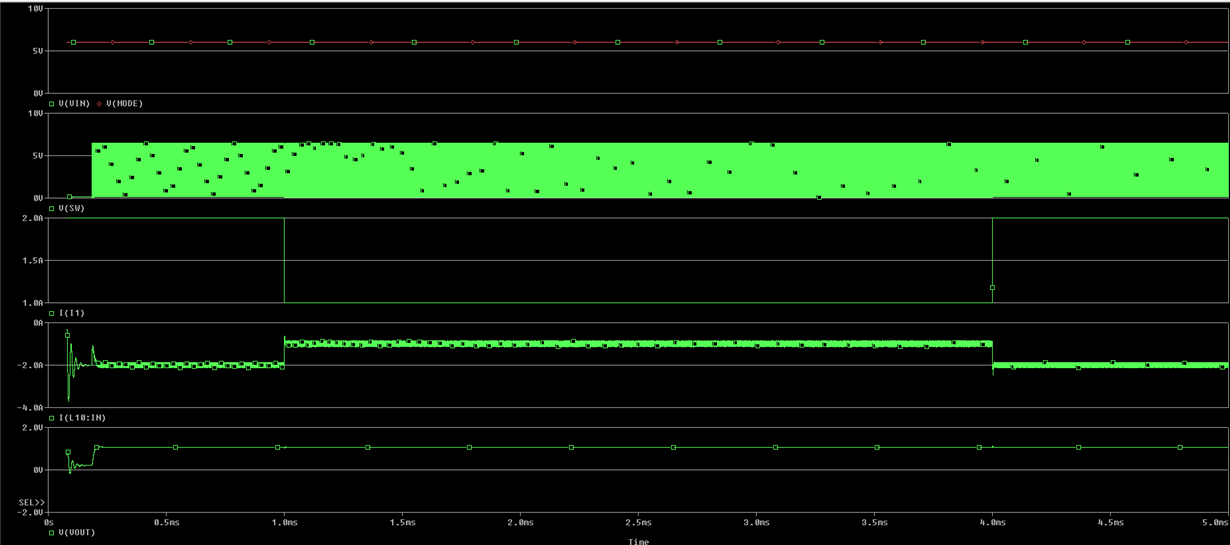

Simulation 1:Change R10 and R11,All other parameters remain the same,Starting the simulation, the VOUT is not 1.1V,

Question 1:Why VOUT is 1.8V?

Simulation 2:Change Iload,All other parameters remain the same,Starting the simulation, the VOUT waveform is abnormal.

Question 1:Why VOUT waveform is abnormal?

Thanks