Other Parts Discussed in Thread: SYSCONFIG

Hi folks,

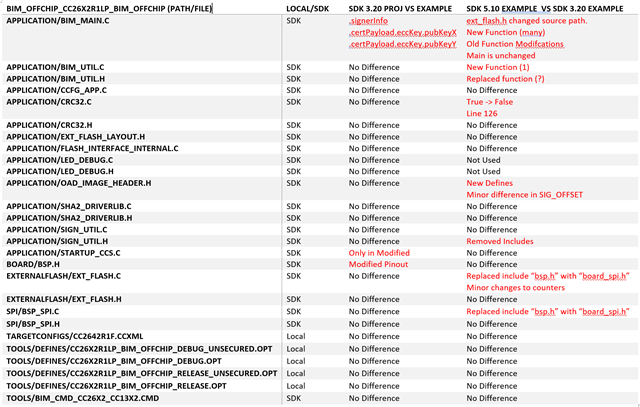

One of the features I have had the most trouble porting from SDK 3.20 to SDK 5.10 has been OAD for both Simple Peripheral Offchip and MultiRole Offchip. Initially, I thought it was user error - but I have come to the conclusion that the SysConfig program is at fault.

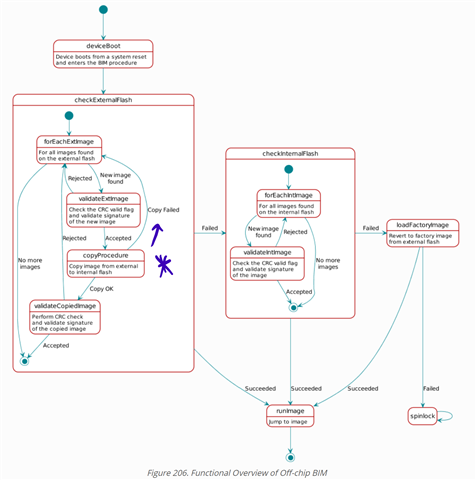

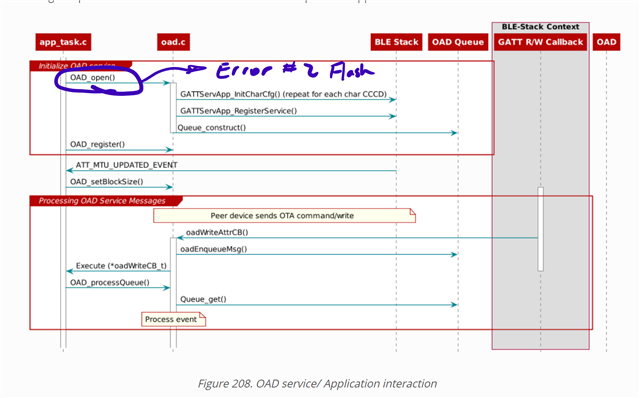

Reference Material from the SDK

Overview

OAD works on both MultiRole and Simple Peripheral project on SDK 3.20. Since SysConfig was not used for this project, I have been migrating to it for SDK 5.10. OAD, while seemingly configured correctly for the BIM project and MR and SP projects, always reports: "OAD failed to open" on the latest SDK.

Diagnosis

I began by configuring the SDK 5.10 SysConfig such that the ti_drivers_config.c and ti_drivers_config.h matched the SDK 3.20 board files as closely as possible.

| SDK 3.20 | SDK 5.10 |

#ifndef Board_EXCLUDE_NVS_EXTERNAL_FLASH

#define SPISECTORSIZE 0x1000

#define SPIREGIONSIZE 0x100000 /* total storage size of external flash */

#define VERIFYBUFSIZE 64

const NVSSPI25X_HWAttrs nvsSPI25XHWAttrs[1] = {

{

.regionBaseOffset = 0,

.regionSize = SPIREGIONSIZE,

.sectorSize = SPISECTORSIZE,

.verifyBuf = verifyBuf,

.verifyBufSize = VERIFYBUFSIZE,

.spiHandle = NULL,

.spiIndex = 0,

.spiBitRate = 4000000,

.spiCsnGpioIndex = CC26X2R1_FLASH_SPI0_CS,

.statusPollDelayUs = 100,

},

};

|

static const NVSSPI25X_HWAttrs nvsSPI25XHWAttrs[1] = {

/* CONFIG_NVS_EXTERNAL */

{

.regionBaseOffset = 0x0,

.regionSize = 0x100000,

.sectorSize = 0x1000,

.verifyBuf = verifyBuf,

.verifyBufSize = 64,

/* NVS opens SPI */

.spiHandle = NULL,

/* SPI driver index */

.spiIndex = SPI_NVS_EXT,

.spiBitRate = 4000000,

/* SPI driver manages SPI flash CS */

.spiCsnGpioIndex = NVSSPI25X_SPI_MANAGES_CS,

.statusPollDelayUs = 100

},

}; |

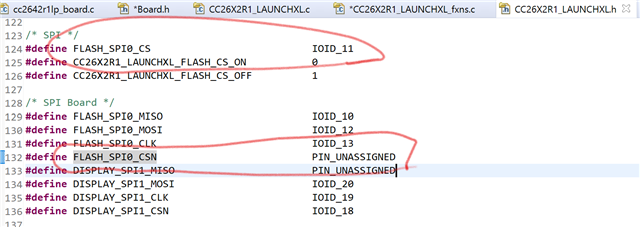

/* SPI */

#define FLASH_SPI0_CS IOID_11

#define CC26X2R1_LAUNCHXL_FLASH_CS_ON 0

#define CC26X2R1_LAUNCHXL_FLASH_CS_OFF 1

/* SPI Board */

#define FLASH_SPI0_MISO IOID_10

#define FLASH_SPI0_MOSI IOID_12

#define FLASH_SPI0_CLK IOID_13

const PIN_Config BoardGpioInitTable[] = {

FLASH_SPI0_CS | PIN_GPIO_OUTPUT_EN | PIN_GPIO_HIGH | PIN_PUSHPULL | PIN_DRVSTR_MIN,

FLASH_SPI0_MISO | PIN_INPUT_EN | PIN_PULLDOWN,

FLASH_SPI0_MOSI | PIN_INPUT_EN | PIN_PULLDOWN,

FLASH_SPI0_CLK | PIN_INPUT_EN | PIN_PULLDOWN,

PIN_TERMINATE

}; |

Pin can be included as part of the SPI object or added to PIN. |

const SPICC26X2DMA_HWAttrs spiCC26X2DMAHWAttrs[CC26X2R1_LAUNCHXL_SPICOUNT] = {

{

.baseAddr = SSI0_BASE,

.intNum = INT_SSI0_COMB,

.intPriority = ~0,

.swiPriority = 0,

.powerMngrId = PowerCC26XX_PERIPH_SSI0,

.defaultTxBufValue = 0xFF,

.rxChannelBitMask = 1<<UDMA_CHAN_SSI0_RX,

.txChannelBitMask = 1<<UDMA_CHAN_SSI0_TX,

.mosiPin = FLASH_SPI0_MOSI,

.misoPin = FLASH_SPI0_MISO,

.clkPin = FLASH_SPI0_CLK,

.csnPin = FLASH_SPI0_CSN,

.minDmaTransferSize = 10

}

} |

const SPICC26X2DMA_HWAttrs spiCC26X2DMAHWAttrs[CONFIG_SPI_COUNT] = {

/* SPI_NVS_EXT */

{

.baseAddr = SSI0_BASE,

.intNum = INT_SSI0_COMB,

.intPriority = (~0),

.swiPriority = 0,

.powerMngrId = PowerCC26XX_PERIPH_SSI0,

.defaultTxBufValue = ~0,

.rxChannelBitMask = 1<<UDMA_CHAN_SSI0_RX,

.txChannelBitMask = 1<<UDMA_CHAN_SSI0_TX,

.minDmaTransferSize = 10,

.mosiPin = IOID_21,

.misoPin = IOID_19,

.clkPin = IOID_20,

.csnPin = PIN_UNASSIGNED

},

}; |

I tired many many things until I noticed a strange behavior - or rather the lack of behavior:

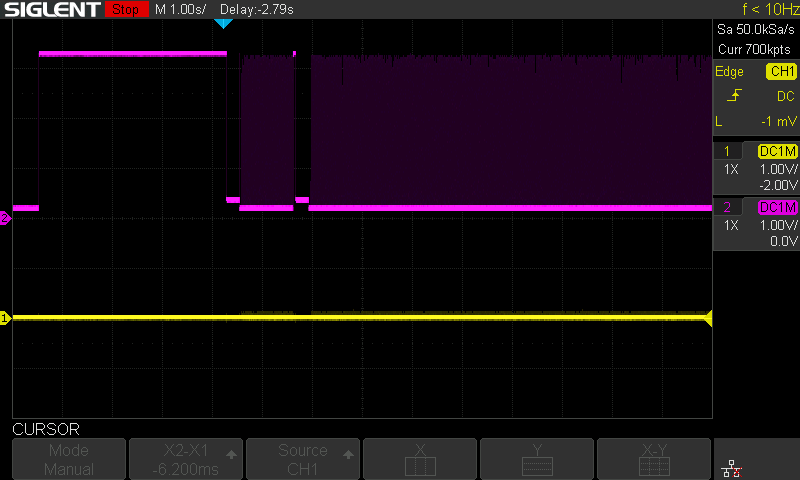

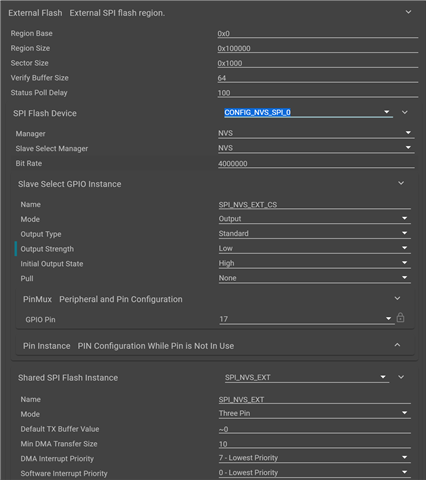

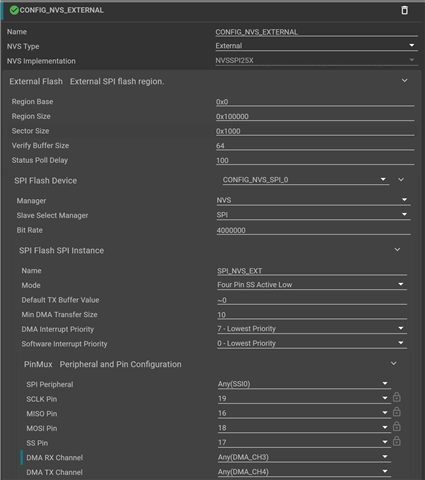

| SDK 5.10 - GPIO Controlled CS | SDK 5.10 - SPI Controlled CS |

|

|

| SDK 5.10 SysConfig Generated: ti_drivers_config.c | SDK 5.10 SysConfig Generated: ti_drivers_config.c |

|

|

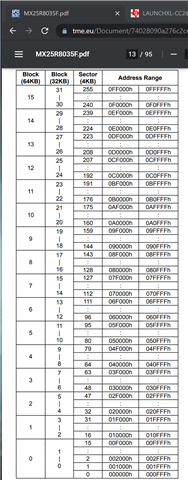

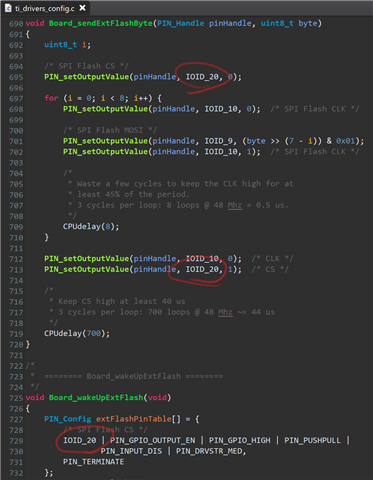

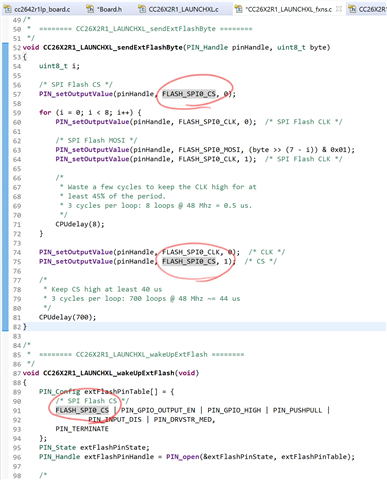

For reference, this is the modified board file for SDK 3.20:

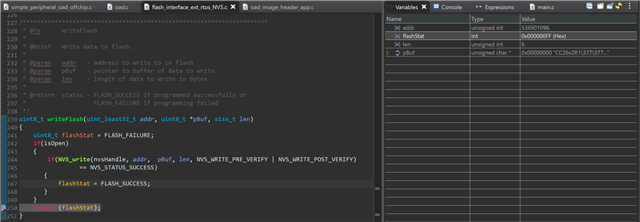

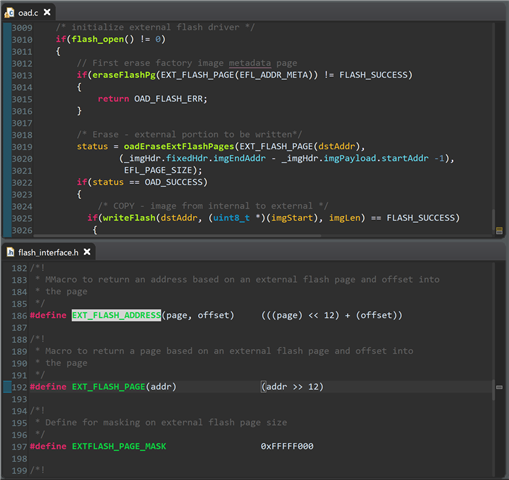

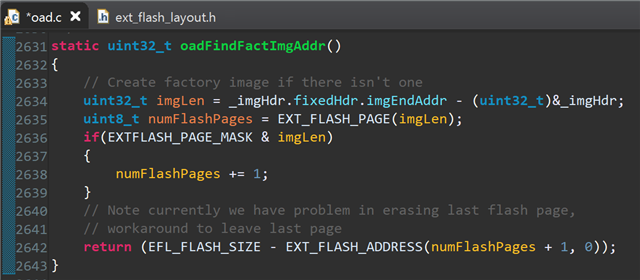

And this depicts the flash specific functions:

The solution for now is to constantly correct this IOID until this bug is fixed. I have been unable to make SysConfig generate a configuration with any other CS Pin IOID which is why I think there is a bug.

Let me know what you think - I have put three days into looking into this bug and only just noticed this behavior.

Best,

Ken