Part Number: CC2640R2F

Hi Team,

Requirement: The coprocessor takes data through SPI every 1ms and sends it to the host processor.

1)

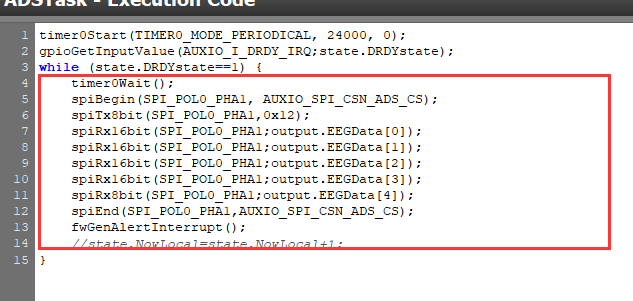

A. If initializing with the following code, using CCS debugging, it can be seen that an SPI request is initiated every 1ms. AUXIO_I_DRDY_IRQ is always high, so the dead loop always runs, fwGenAlertInterrupt wakes up and the main processor scTaskAlertCallback does not execute.

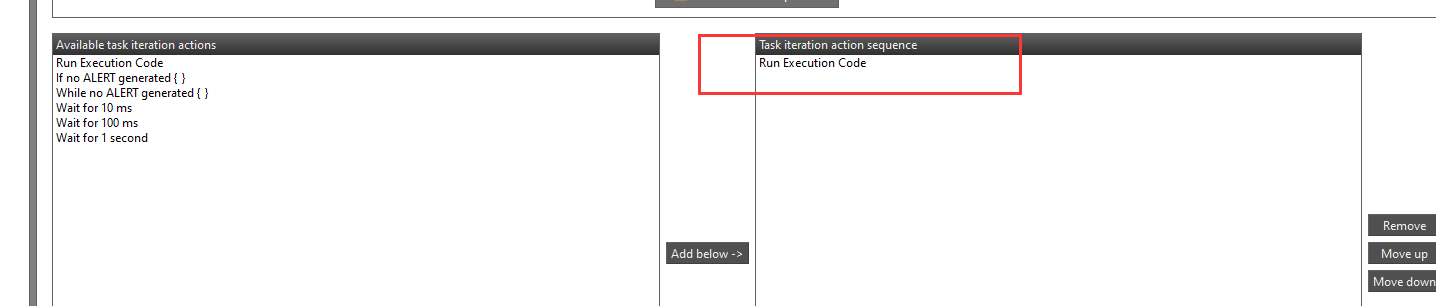

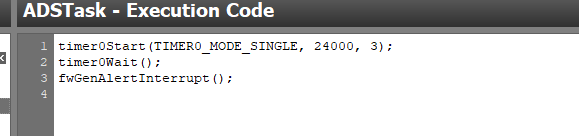

B. The customer wakes up the system to move it as shown in the following code. Toggle level every time scTaskAlertCallback is executed, use the 1-pin test of the logic analyzer, theoretically it should not flip. but the logic analyzer was only executed once. Why's this?

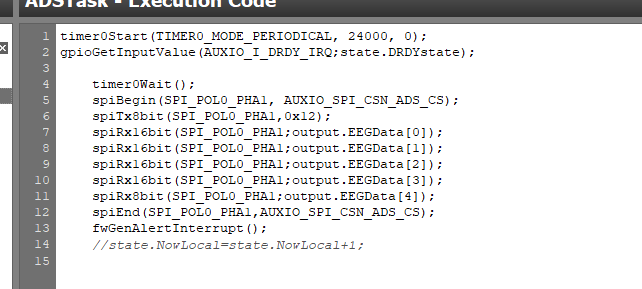

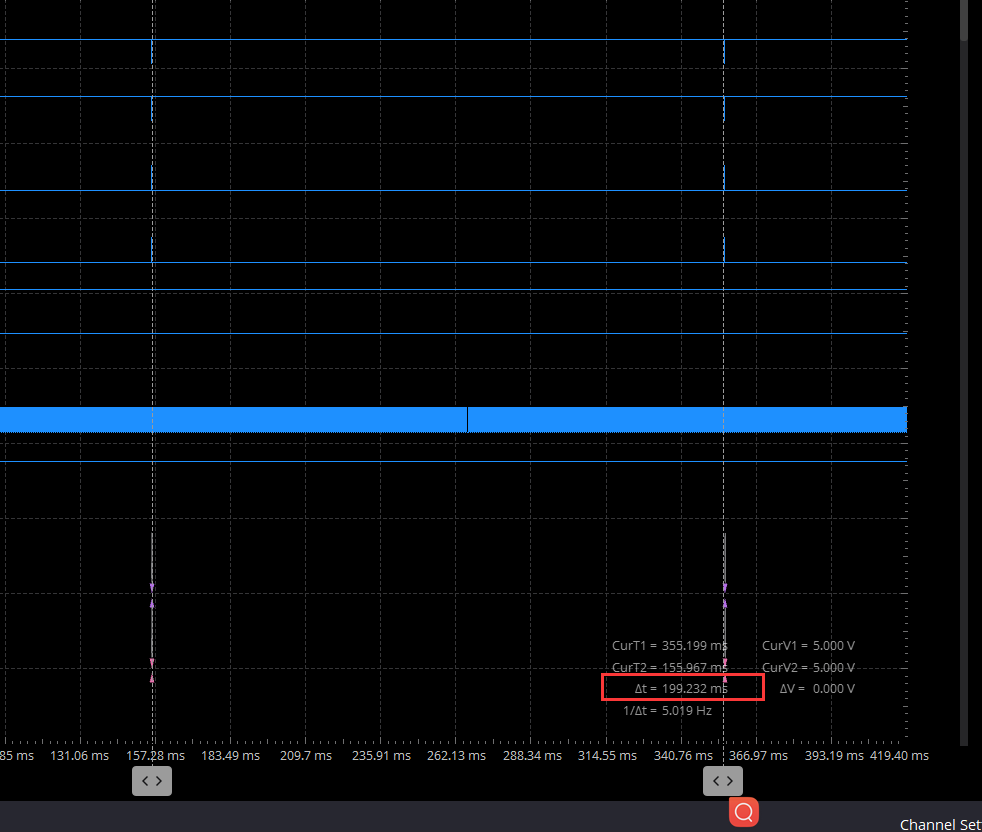

C. By removing the dead loop into the following code, it can be seen from the logical analysis that the data is not taken every 1 ms. Why?

D. The above data is captured by the logic analyzer in the CCS development tool debug mode, when the code is ported and the coprocessor and M3 work together, compare the figure of the above question C, you can see that the SPI signal cannot be captured, but the signal toggles when scTaskAlertCallback is acquired. The figure above(Question C) captures the SPI signal, but cannot capture the signal that toggles when scTaskAlertCallback is active. The signals that can be captured during debug and runtime of the CCS development tool are the opposite. It is hard to determine exactly what the SPI signal looks like when the system is running properly after the code is ported.

2) Based on the above picture of the logic analyzer, it can be basically determined that scTaskAlertCallback is executing. Takes the SPI data out and sends it to the host, but strange that the host receives exactly the same data.

3) Based on the green data for question 2, the difference is because the customer manually changed the first data at the time of the test. Code D2 should be followed by D3, and this becomes D4 on the host. And the problem is common, and there is even a case where E8 is followed by 44. Why's this?

Could you please help check this case? Thanks.

Best Regards,

Cherry