Other Parts Discussed in Thread: UNIFLASH,

Hi,

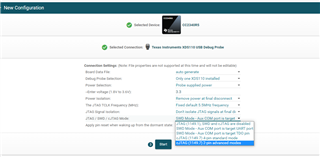

Up until now we have been using the UniFlash PC software and XDS110 Programmer to flash program the CC2340R5, we have been interfacing with the VDD, GND, SWDIO, SWDCK and nRST pins. However due to some issues with latest samples we no longer have easy access to nRST. Now when we try to program we get errors from Uniflash software.

Therefore I was wondering is it possible to change the programming setup to work around not having access to nRST?

Thanks

Andrew