Other Parts Discussed in Thread: SYSCONFIG

Hi all,

Software: example "project zero" project. Vanilla, no modifications.

Hardware: cc26x2r launchpad.

The following code modification at the end of function "project_zero_init()" allows my oscilloscope to see the 32 kHz crystal clock signal rerouted to launchpad upper right GPIO 12. Neat! Thanks to Clement.

IOCPortConfigureSet(12, IOC_PORT_AON_CLK32K, IOC_STD_OUTPUT);

AONIOC32kHzOutputEnable();

This signal is more or less OK but it is not accurate enough for our purposes. We would like to adjust it per device. So, just before the previous code, we add:

uint32_t subSecInc = 0x20000;

HWREG( AUX_WUC_BASE + AUX_WUC_O_RTCSUBSECINC0 ) = (( subSecInc ) & AUX_WUC_RTCSUBSECINC0_INC15_0_M );

HWREG( AUX_WUC_BASE + AUX_WUC_O_RTCSUBSECINC1 ) = (( subSecInc >> 16 ) & AUX_WUC_RTCSUBSECINC1_INC23_16_M );

HWREG( AUX_WUC_BASE + AUX_WUC_O_RTCSUBSECINCCTL ) = AUX_WUC_RTCSUBSECINCCTL_UPD_REQ;

while( ! ( HWREGBITW( AUX_WUC_BASE + AUX_WUC_O_RTCSUBSECINCCTL, AUX_WUC_RTCSUBSECINCCTL_UPD_ACK_BITN )));

HWREG( AUX_WUC_BASE + AUX_WUC_O_RTCSUBSECINCCTL ) = 0;

Unfortunately, this code gets stuck in the while loop. I suspect my offset for AUX_WUC_O_RTCSUBSECINCCTL is wrong, so the combination UPD_REQ, UPD_ACK is never satisfied.

I visited a similar thread but the answer there did not make me go past the loop . I attach it here for the sake of convenience for other people.

e2e.ti.com/.../cc1310-c1310-hang-on-change-rtc-sub-second-increment

My intention is to modify the value subSecInc, for example to 0x20004 to compensate the crystal signal and obtain better precision. This would only be done at the beginning of the code. We would obtain this 0x20004 value or similar via tests by using a frequency counter per device and then load it.

So, my question is twofold:

- The register view in Code Composer Studio does not show me any AUX_WUC_O_RTCSUBSECINCCTL, is my offset address right? Please see the #defines I made at the end of this post.

- Is this the proper place where to put this calibration code?

Please, let me know your points of view to both questions. The #defines come next.

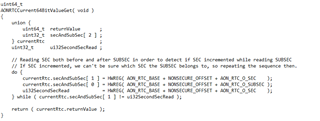

#include <driverlib/aon_ioc.h> #define AUX_WUC_BASE 0x400C6000 #define AUX_WUC_O_RTCSUBSECINC0 0x0000003C #define AUX_WUC_O_RTCSUBSECINC1 0x00000040 #define AUX_WUC_O_RTCSUBSECINCCTL 0x00000044 #define AUX_WUC_RTCSUBSECINC1_INC23_16_M 0x00FF0000 #define AUX_WUC_RTCSUBSECINC0_INC15_0_M 0x0000FFFF #define AUX_WUC_RTCSUBSECINCCTL_UPD_ACK_BITN 0x02 #define AUX_WUC_RTCSUBSECINCCTL_UPD_REQ 0x01

Have a really nice day.