Other Parts Discussed in Thread: CC1354P10, SYSCONFIG

Tool/software:

Hi,

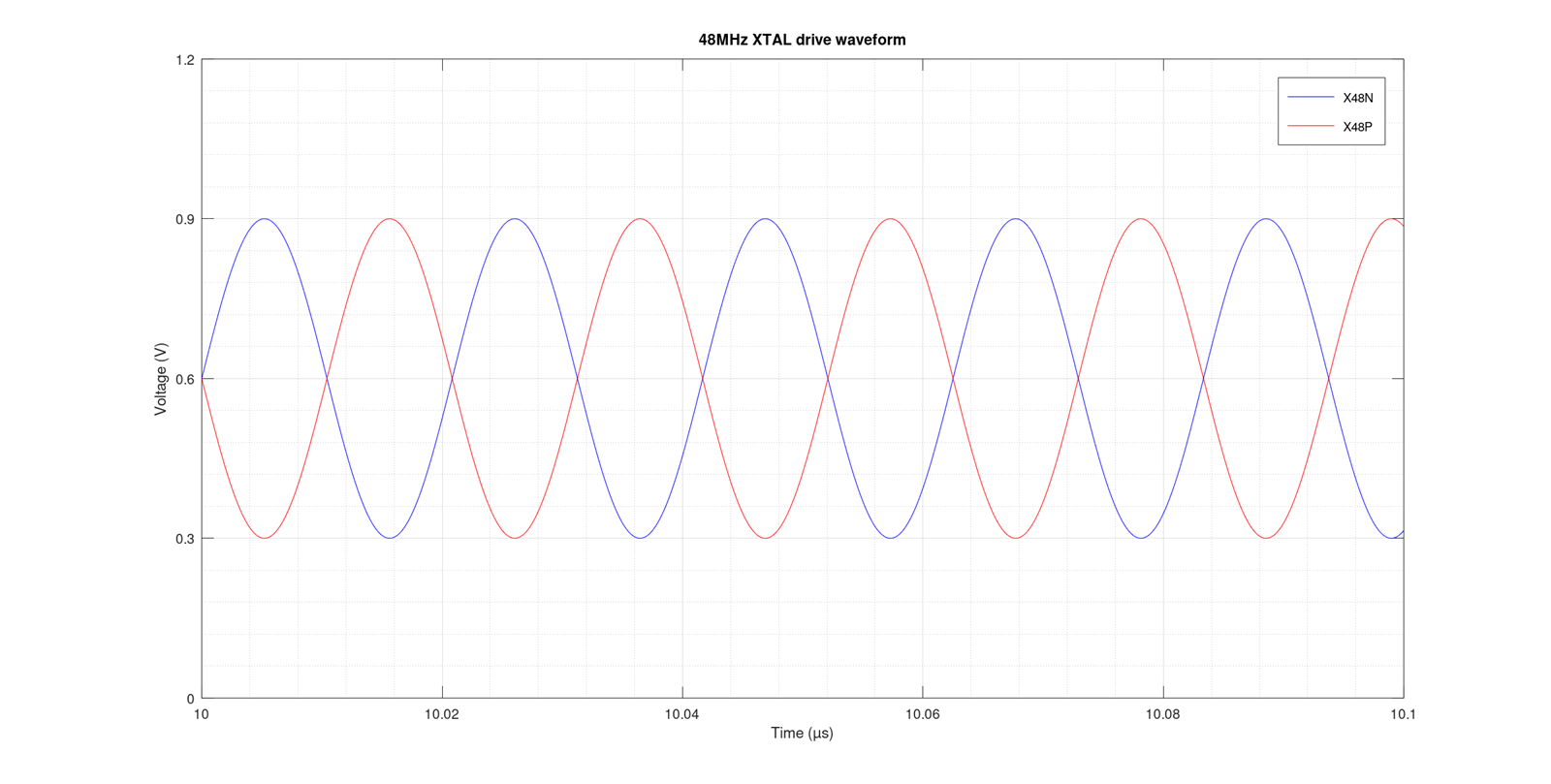

Section 3.5 > "The CC13xx and CC26xx devices drive the crystal with a maximum 1.6 Vpp_differential for the 24/48-MHz"

> Drive level formula : DL = 2 x ESR (πf(CL + C0) Vpp)² ;

The CC1354P10_6 EVM uses the TZ3780AAAO44 with ESR = 30Ohms, CL = 7pF, Co = 3 pF, 48 MHz. The document says Vpp_diff = 1.6V so the DL = 349 µW > 200µW (max recommended)

Would make more sense if the Vpp in the DS is the single-ended at one of the pins of the quartz.

Finally, using the on-board ADC (section 5) I get the value ~430mV.

- Vpp in the drive level formula is single-ended, correct ?

- Is ~430 mV an excepted value for Vpp?

Thanks,

Geoffrey