Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

Hi team,

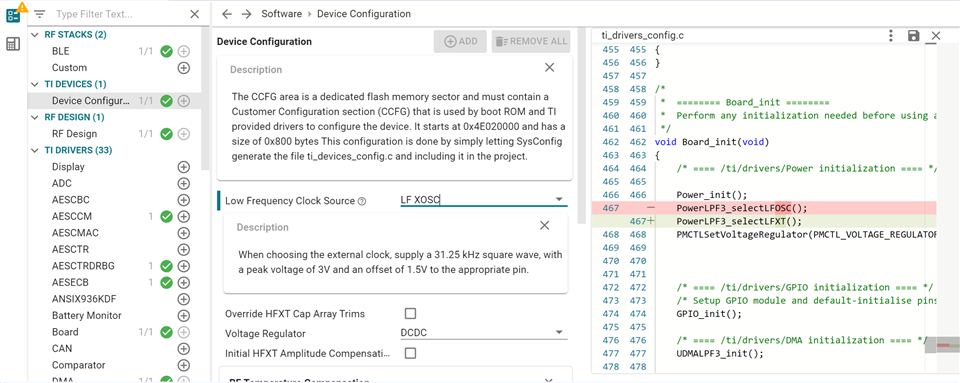

Customer is switching from using the internal low frequency clock to the external clock. Their external clock is running at 32.768kHz but the note inside of Sysconfig (version 1.20.0) looks like it is saying that it should be running at 31.25kHz. Is this right or is this a typo in the description? If correct, could you explain?

The LF crystal and LF osc are both 32.768kHz, so it doesn't make sense to me that the External LF would not also be 32.768kHz. I also can't find any reference in the datasheet or TRM for this 31.25kHz clock requirement.

Thanks,

Luke