Other Parts Discussed in Thread: UNIFLASH, SYSCONFIG

Tool/software:

Hello TI support Team,

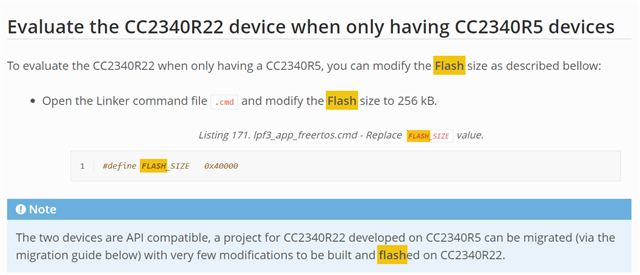

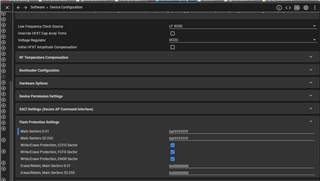

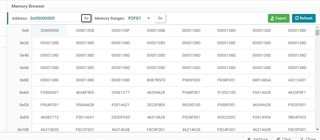

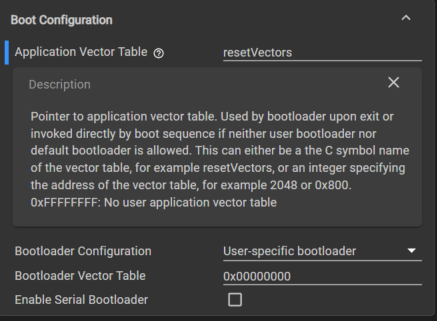

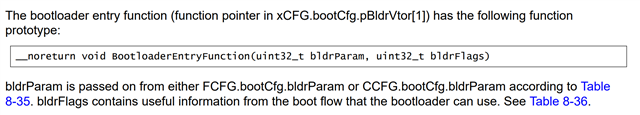

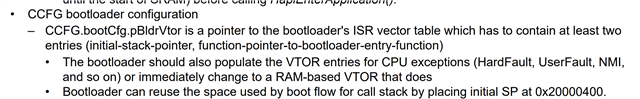

I plan to allocate the bootloader's flash memory block from address 0x00000000 to 0x0000FFFF and designate address 0x00010000 as the application start address.

So I modified "FLASH_BASE" in lpf3_freertos.cmd file.

=========================================================

Cortex_M0P: Failed to remove the debug state from the target before disconnecting. There may still be breakpoint op-codes embedded in program memory. It is recommended that you reset the emulator before you connect and reload your program before you continue debugging"

Thank you for your guidance.