Other Parts Discussed in Thread: LP-EM-CC2340R5

Tool/software:

Hi, TI Team.

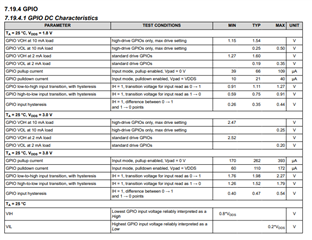

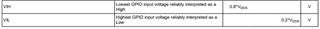

In the datasheet, there are conditions for the duration of the signal, but no conditions for the signal level.

At what voltage level will the signal trigger a reset?

Additionally, please let me know if there are any constraints regarding hysteresis and the rise time when resetting returns.

Regards.