Tool/software:

Hello team,

I need to understand the current consumption of CC2745R10 , when the BLE is in advertising mode .This will help us to calculate system level sleep current for the complete ECU

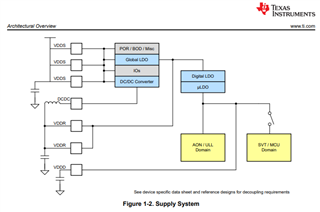

I am using the internal Buck regulator to supply VDDR