Other Parts Discussed in Thread: UNIFLASH, , SYSCONFIG

Tool/software:

Hi TI Support Team,

I am working on protecting important data in flash when using BLDR_CMD_CHIP_ERASE

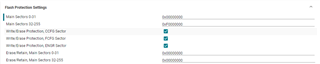

I enabled the flash protection and do a test.

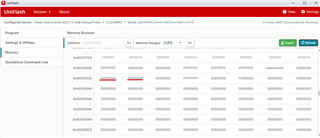

My Flash Protection Settings are shown in the image below:

Test Scenario:

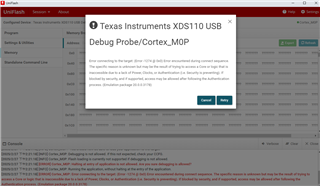

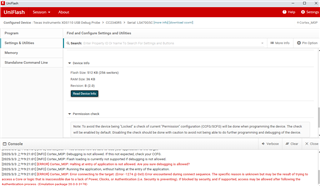

- I enabled flash protection in my application and booted into the ROM bootloader.

- A host sent the

BLDR_CMD_CHIP_ERASEcommand to the device and downloaded only the CCFG.

According to the Technical Reference Manual (TRM) section "8.5.3.5 BLDR_CMD_CHIP_ERASE", it seems possible to specify certain flash sectors to retain from a bootloader erase:

| This command is used to perform a chip erase of the device. All main flash bank sectors not protected by FCFG and CCFG protect bits are erased. The CCFG is erased once the bank erase has completed. This command first invalidates the CCFG and then begin erasing all unprotected sectors in the main flash bank. Once the flash sectors have been erased, the command finally erases the contents of the CCFG. |

Based on my flash protection settings, my application should not have been erased.

However, after running the test, I found that my application was erased.

Could you provide guidance on implementing proper write protection when using BLDR_CMD_CHIP_ERASE?

Thank you for your support.