Part Number: LP-EM-CC2340R5

Other Parts Discussed in Thread: CC2340R5, , SYSCONFIG

Tool/software:

Hey folks! I'm sure there's a more productive way to debug this, and I'm struggling to find it.

I've been following: Debugging — SimpleLink CC23xx SDK BLE5-Stack User's Guide 3.02.04.00 documentation

Here's what I know so far:

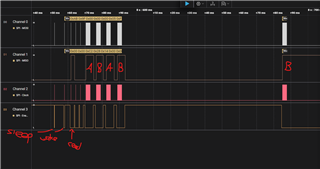

- SPI transfers are successful and work (healthy transactions, what I expect, data is read back successfully too)

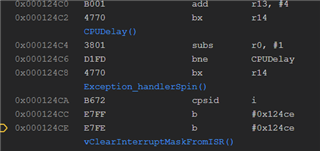

- Consistently, the next SPI transfer puts me into ExceptionArmV6M.c 's Exception_handlerSpin. Identical to the image above.

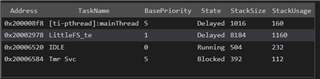

- Looking at tasks, none exceed stack size

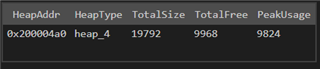

-Heap seems fine

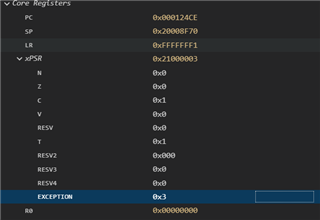

- Looking at PC program counter, 0x000124CE, which points me to this exception_handlerSpin, makes sense

- xPSR confirms yes, this is a hard fault via 0x3

- MSP / SP are the same 0x20008F70 value. Looking at this address in disassembly doesn't lead me to anything fruitful. No functions nearby /above to give me hints.

- Logging, my code is essentially, where the last log is immediately after spi_transfer:

log (start SPI transfer) //this prints to log spi_transfer(stuff) //SPI trasnfer completes via Saleae reading log (end SPI transfer) //never prints

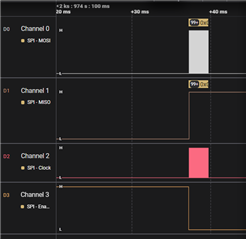

So I'm not sure how to debug from here... Looking at the SPI and DMA registers,

DMA -> ERROR: 0x00000000

SPI0 -> raw interrupt status: IDLE and TX 0x1

SPI0 -> STA: RX FIFO not full, it's empty. TX FIFO not full, it's empty

Any thoughts or wisdoms appreciated!