Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Sir,

I am using the LAUNCHXL-CC26X2R1 board to communicate with an external L9963E IC via SPI.

My project uses the TI SPI Driver (SPI.h) from SimpleLink CC13xx CC26xx SDK

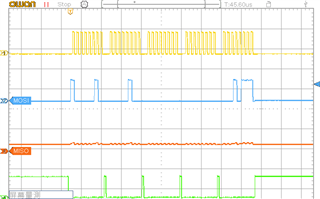

I have encountered an issue when operating in SPI_POL0_PHA0 mode (CPOL=0, CPHA=0):

Even though I set transaction.count =5 , the CS pin is pulled high after each byte, causing the transfer to be split into multiple segments.

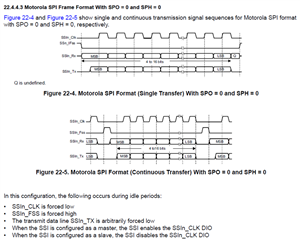

I am not sure if this behavior is related to the Single Transfer or Continuous Transfer modes mentioned in the TRM (Chapter 22.4.4.3), but I couldn't find any configuration option in the TI SPI Driver (SPI.h API) to change this behavior.

I would like to know where to change this setting—whether via an API, SysConfig, or by modifying the low-level driver source code.