Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

My customer is trying to develop a high performance UART to BLE bridge application on CC2340R5. The design goal is to steady work under 460800 baud rate. To improve the performance a ring buffer is used to store the received UART data, BLE application will retrive data from this ring buffer and send through BLE notification to the peer device.

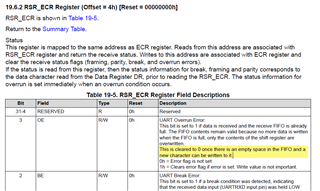

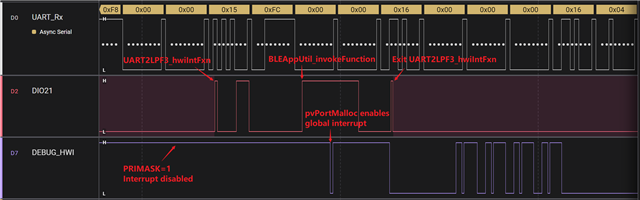

The application is working fine with 115200 baud rate, but when the baud rate increased to 460800, missing bytes are seen at the UART Rx side.

- The bytes are directly missed from UART Rx buffer. CC2340 UART never received these bytes. This is verified from a count of received bytes in UART callback.

- If BLE and the ring buffer is not used(only receive UART data but not put it into the ring buffer), the issue does not happen.

- If ring buffer is used but BLE is not(put received data into ring buffer but does not send through BLE notification), the issue still happens.

The customer has a project to reproduce this issue(please reach out to me offline for the project). To reproduce the issue, please follow the steps:

- Run the project on a CC2340R5 LaunchPad.

- Connect to a cellphone.

- Request an MTU of 247 bytes from the phone.

- Enable notification from the phone.

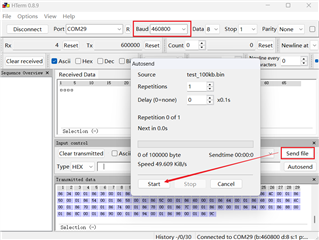

- Open a UART terminal(hTerm) using 460800 baud rate.

- Send a file(I created a 100kB sample file as attached below) through UART to CC2340.

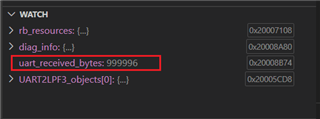

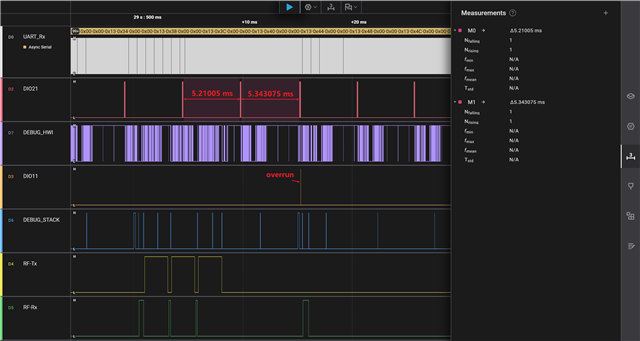

- Watch for uart_received_bytes in CCS watch window.

Repeat step 6 and 7 and watch for the uart_received_bytes variable, each time the UART terminal sends 100,000 bytes to CC2340, and once in a while uart_received_bytes will be one or two bytes less than the sent bytes.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/538/test_5F00_100kb.bin

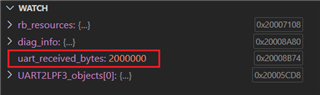

It looks the issue is related to the interrupt priority or DMA transfer, but I am having trouble locating the exact location of the issue. I have tried to adjust the UART HWI priority and the UART ring buffer size, but both did not make a difference. Would you please help locate the root cause? Thanks.

Best regards,

Shuyang