Tool/software:

Hi Team,

My customer is using CC2340R5-Q1 and is running ESD test.

They found when ESD Fail, CC2340R5-Q1 will not reset even the 30sec Watchdog timer is enabled.

(SDK Version is :8_20_00_119)

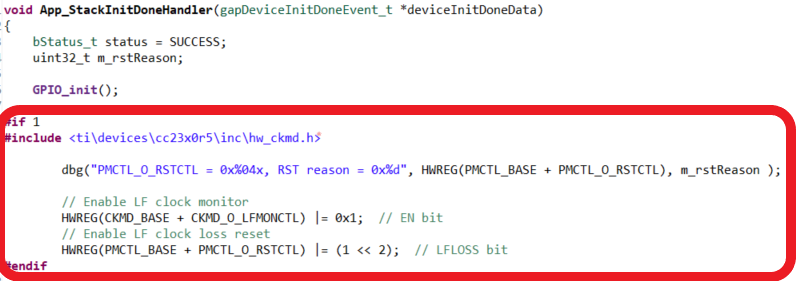

By TRM 6.7.2, we try to enable LF Loss detection and enable LF clock loss reset, and the following is the code:

void enableLFClockLossDetection(void) {

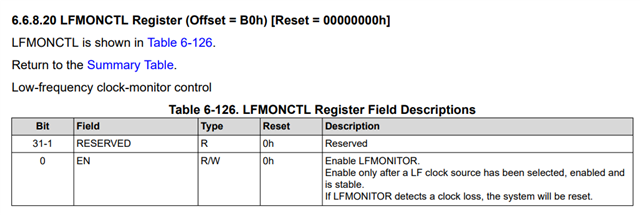

// enable LF clock monitor

HWREG(CKMD_BASE + CKMD_O_LFMONCTL) |= 0x1; // EN bit

// enable LF clock loss reset

HWREG(PMCTL_BASE + PMCTL_O_RSTCTL) |= (1 << 2); // LFLOSS bit

}

My customer report that they will get error when using above code.

Please help to provide suggestion for us to debug this issue.

Or provide some comment for us to check what procedure need to be handled before enabling LF Loss detection and LF clock loss reset.