Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi team

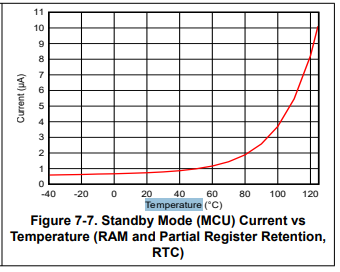

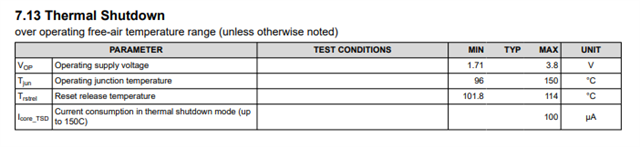

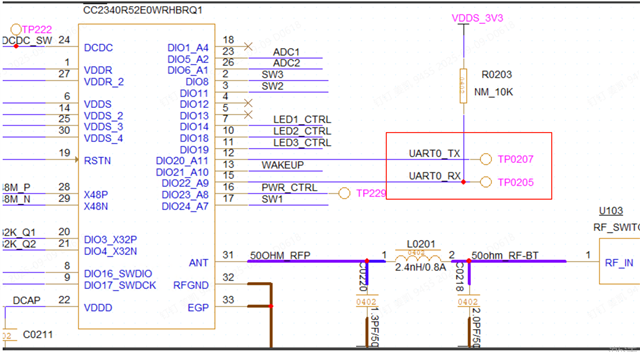

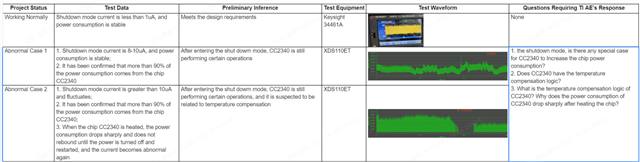

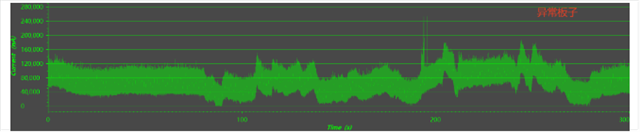

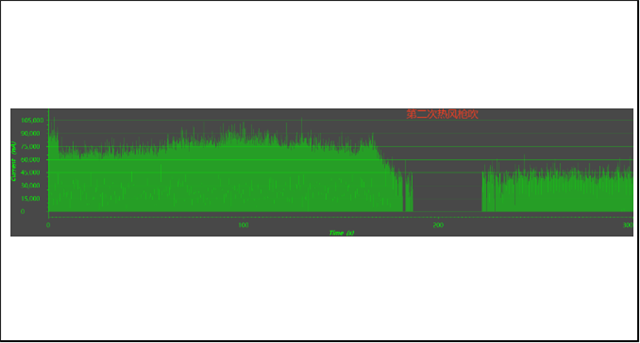

I have found that some chips have power consumption issues and need help to analyze them. The test data is as follows:

SDK:8.10

question:

1. the shutdown mode, is there any special case for CC2340 to Increase the chip power consumption?

2. Does CC2340 have the temperature compensation logic?

3. What is the temperature compensation logic of CC2340? Why does the power consumption of CC2340 drop sharply after heating the chip?